- 全部

- 默认排序

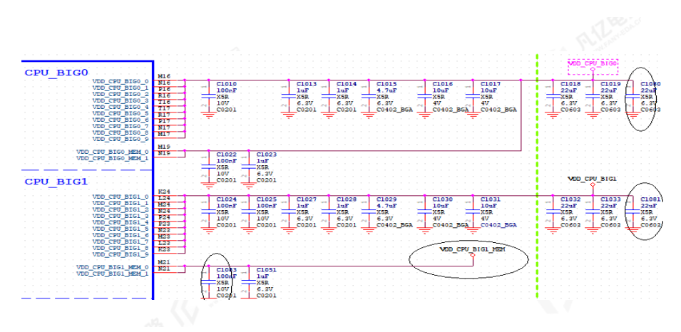

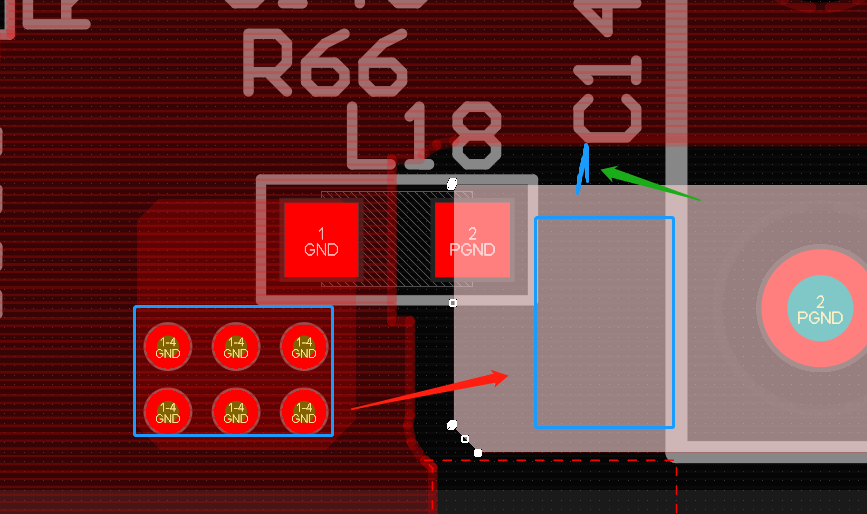

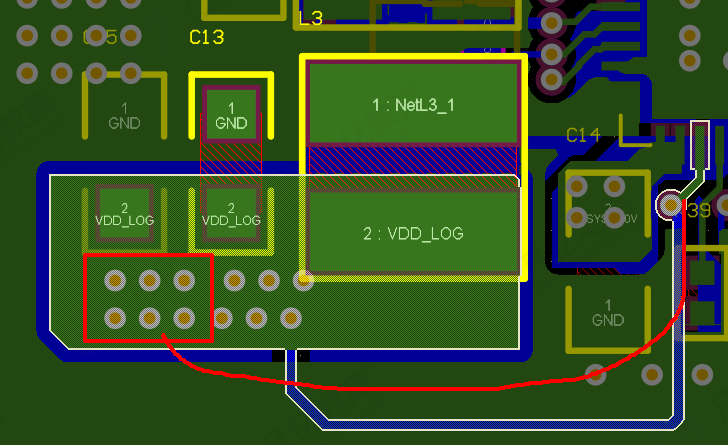

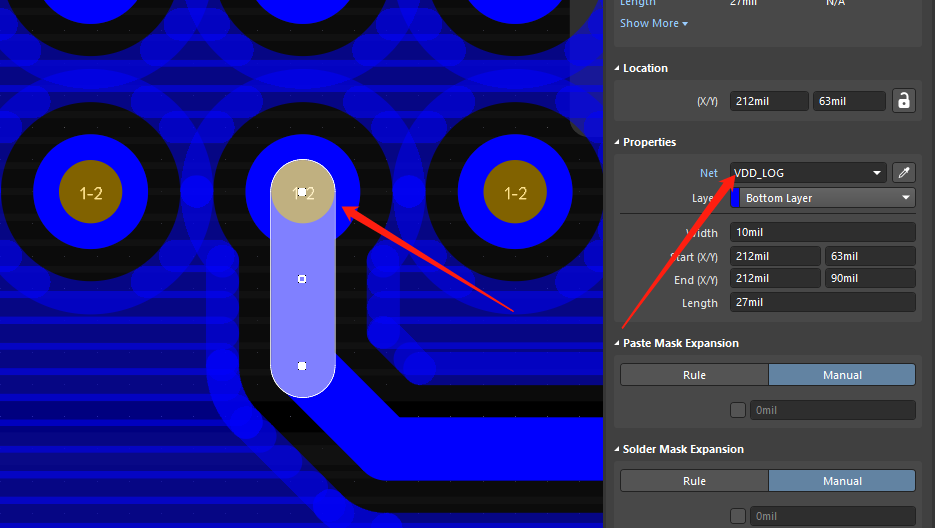

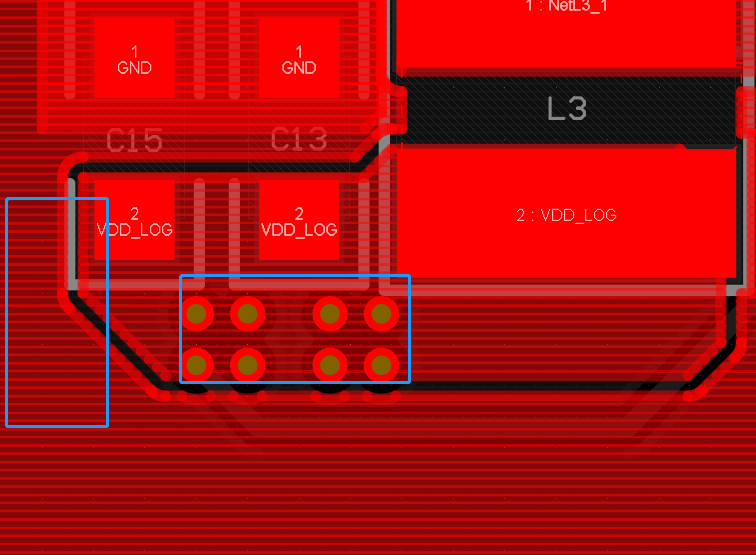

RK3588 VDD_CPU_BIG0/1 电源PCB设计1、如图1所示的滤波电容,原理图上靠近 RK3588的VDD_CPU_BIG电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容GND PAD尽量靠近芯片中心的GND管脚放置,

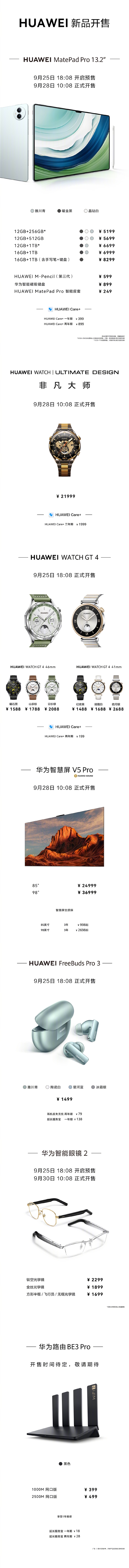

9月25日,华为全场景新品发布会如期举行,在该发布会里华为一口气推出了七大新品,涵盖了多个应用场景。与此同时,Mate 60全系、Mate X5、AITO问界M5全系、新M7系列等全面开售。1、华为MatePAD Pro 13.2英寸平板颜

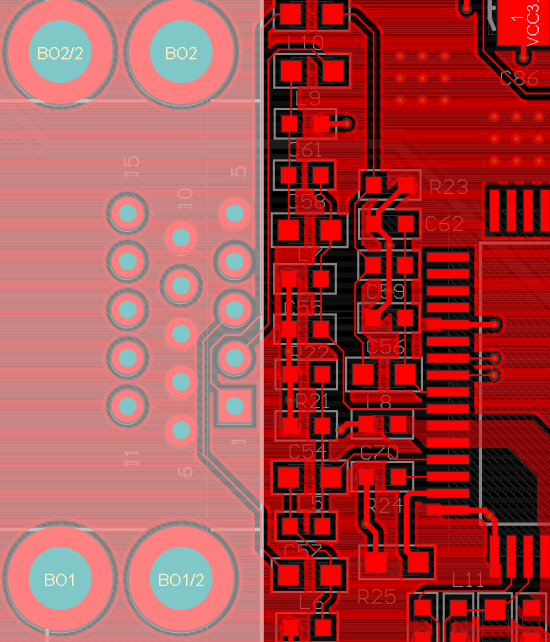

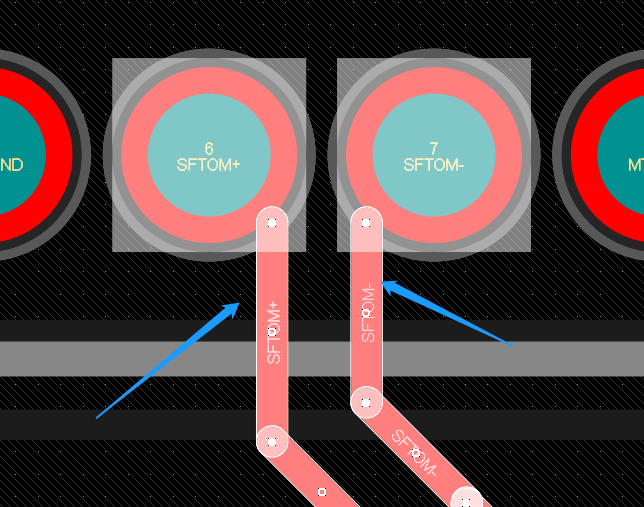

VGA模拟信号要一字型布局,走线加粗处理2.晶振需要走内差分,走线要尽量短,晶振尽量顶层走线,包地要包完整3.差分对内等长不能超过线距的两倍,包地要在地线上打孔4.跨接器件旁边需要多打地过孔,器件摆放可以在优化一下5.反馈需要从最后一个电容

跨接器件旁边要尽量多打地过孔,地分割间距最少1.5mm2.网口差分要进行对内等长,误差5mil3.模拟信号走线需要加粗4.地网络要就近打孔,回流到地平面5.反馈信号压迫从电容后面取样,走线要加粗6.注意数据线之间等长需要满足3W规则7.等长

1.过孔应打到最后一个器件的后方,反馈信号需要连到最后一个电容。2.多处过孔上焊盘3.电源信号连接处铜皮需要加宽载流4.多处孤岛铜皮和尖岬铜皮5.注意保持过孔之间间距和过孔到焊盘间距不能太近6.电源信号走线需要加粗保持前后线宽一致7.走线不

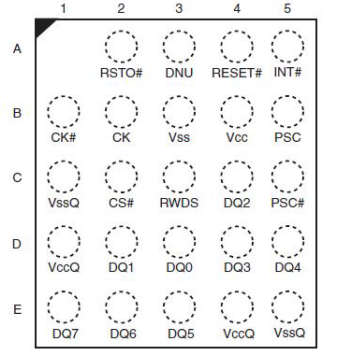

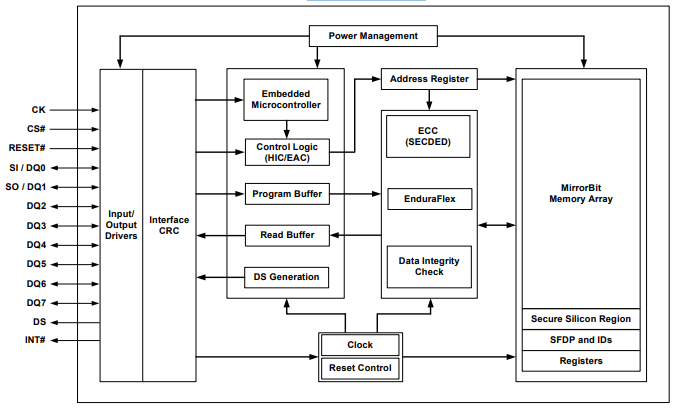

一、HyperFlash NOR 闪存概述S26KS128S(128Mb)HyperFlash™ NOR闪存采用小型 8x6mm 球栅阵列 (BGA) 封装,与 QuAD SPI 和双 QuAD SPI 部件共享一个共同占位面积,以简化电路

一、简介S28HL512T (512Mb)NOR闪存集成了用于汽车和工业系统的安全特性。应用包括汽车仪表盘、高级辅助驾驶系统 (ADAS) 以及网络通信。该款NOR闪存符合汽车功能安全标准,以及ASIL-B和ASIL-D标准。二、Logic

走线尽量从焊盘中心出线,避免造成开路2.差分出线要尽量耦合3.注意布局需要满足原理图规范4.注意确认此处是否满足载流5.电容尽量一个管脚一个,靠近摆放6.走线尽量不要从小器件中心穿,后期容易造成短路7.晶振尽量包地处理8.存在多处开路过孔不

存在无网络过孔,短路了2.输出过孔要打在最后一下滤波电容的后面3.过孔不要上焊盘4.电感下面尽量不要放置器件和走线5.存在多处开路和drc报错,后期自己处理一下6.注意走线需要连接到焊盘中心,此处需要优化一下7.相同网络的走线和铜皮未进行连

输出打孔要打在滤波电容后面2.此处不满足载流,载流是一铜皮最窄出计算的,后期自己加宽一下铜皮3.铺铜是尽量把焊盘包裹起来,这样容易造成开路4.存在多处开路和drc报错5.电感下面不要走线和放置器件6.注意中间散热焊盘上的过孔需要开窗处理7.

扫码关注

扫码关注