- 全部

- 默认排序

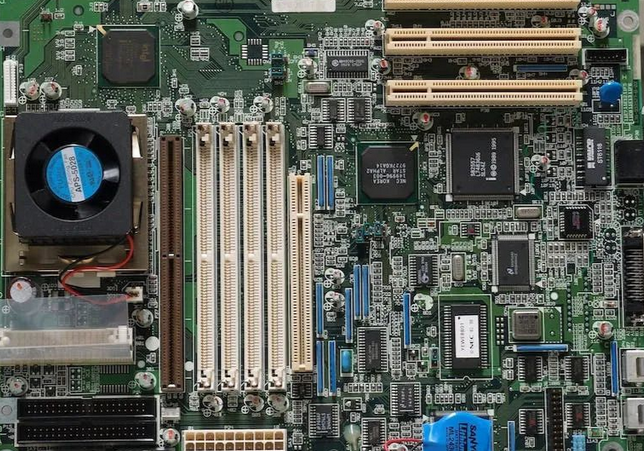

在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰

随着半导体技术高速发展,越来越多电子产品迭代更新速度加快,高速度的数据传输及内存支持,这些都离不开DDR产品的支持,DDR产品已成为了大部分电子工程师的日常设计产品之一。然而DDR产品的设计是具有挑战性的,因为它涉及到高速数字电路和复杂的时

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

在电磁兼容性设计中,信号反射是电子工程师的重要考虑因素之一,特别是在高速数字系统中,信号反射可导致多种问题,如过冲、下冲和振铃,针对这些问题如何分析,并制作相关的电路设计?首先,这些问题的发生,原因在于是由信号在传输线上传播时遇到阻抗不匹配

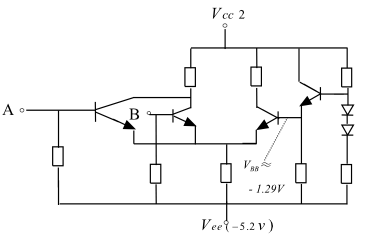

高速数字电路应用广泛,是电子工程师及小白需要重点学习并运用的电路,但有很多人就会很好奇高速数字电路种类那么多,有哪种?所以本文将搜集平台内容,分享常见的高速数字电路,希望对小伙伴们有所帮助。1、ECL(Emitter Coupled Log

信号传输的速率越来越高,对网络带宽的需求越来越高,高速高频电路逐渐替代低速电路成为主流。可以说,现在是属于高速数字的世界,未来将需要大量的懂高速电路设计的人才。高速电路的核心是信号完整性,学信号完整性,必然也有信号仿真,信号仿真是很多电子工

在高速数字电路设计中,过孔的寄生电感问题是电子工程师经常面对的问题之一,寄生电感的存在很容易影响电路的性能,甚至引发意想不到的问题,因此必须及时计算电感然后解决问题,那么如何计算?首先在计算寄生电感问题之前,必须先了解寄生电感到底是什么?简

提起差分信号,很多电子工程师都不会陌生,得益于高速数字信号传输中的广泛应用,差分信号的走线在PCB设计中具有重要地位,为了确保差分信号的完整性,工程师需要遵循一些特定的规则,身为工程师的你知道有哪些规则吗?1、相对路径长度匹配差分信号对的两

在PCB设计过程中,若是在电源平面或地平面的分割处理不当,很容易导致平面的不完整,信号走线时,其参考平面将出现在一个电源面跨接到另一个电源面,这种现象叫做信号跨分割。跨分割对低速信号影响不大,但在高速数字信号系统重影响很大,所以电子工程师该

凡亿深圳pcb培训讲解PCB设计走线时注意事项总结如下: 1. 一般规则 1.1 PCB板上预划分数字、模拟、DAA信号布线区域。 1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。 1.3 高速数字信号走线尽量短。 1.4 敏感模拟信号走线尽量短。 1.5 合理分配电源和地。

扫码关注

扫码关注