- 全部

- 默认排序

一个完整的原理图文件,需要发给别人查看某一个模块原理图或某一页原理图时,为了原理图文件的保密性考虑,可以利用软件输出PDF格式的文件,方便别人进行查阅。通过视频中的讲解一起来学习下logic软件怎样导出PDF格式文件。

PCB设计时,有时候需要在不增加PCB走线宽度的情况下提高该走线通过大电流的能力(载流能力),通常的方法是给该导线镀锡(或者上锡);下面以在PCB顶层走线镀锡为例,使用AD20软件,简单介绍如何走线上锡处理。

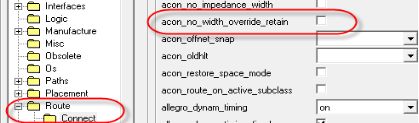

答:在Allegro PCB中,会经常切换走线线宽,一般Allegro PCB默认是记忆走线线宽的,即走完一个信号在连接一个新的网络线时,软件会默认使用连接上一个网络所使用的线宽。可以通过设置,让软件不执行自动记忆上一次走线宽度。

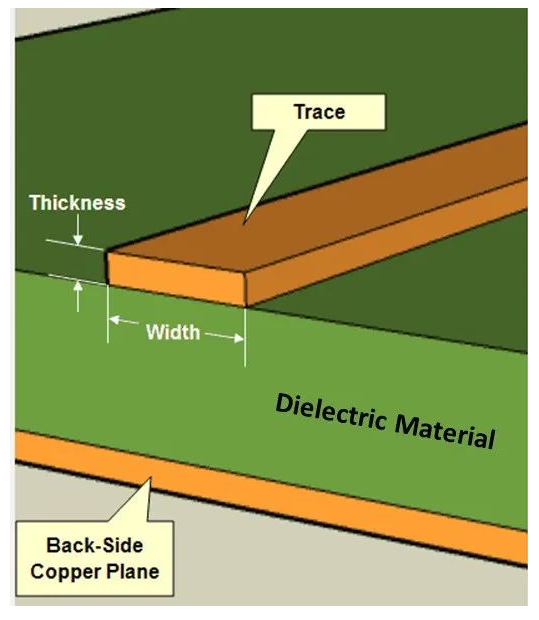

当涉及到PCB 设计时,PCB 走线电流容量带来的限制是至关重要的。虽然IPC-2221通用设计指南是一个很好的起点,但 PCB 走线宽度计算器提供了可用于电路板设计的准确值。PCB上一条走线的电流容量由走线宽度、走线厚度、所需的最大温升、

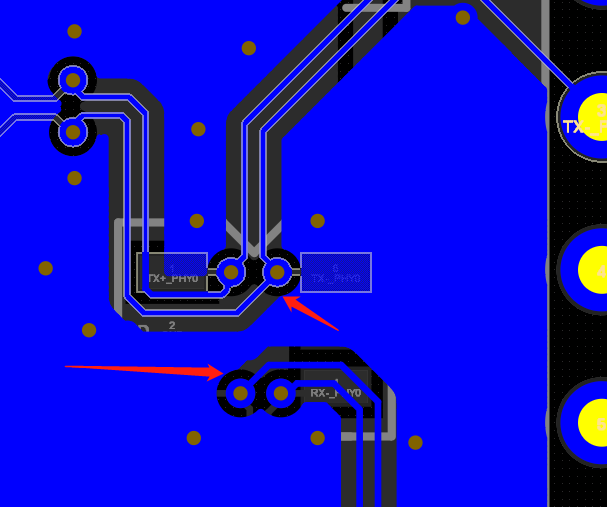

1.多处焊盘出线问题,焊盘中心出线至外部才能拐线处理。2.过孔没有网络3.焊盘出线尽量耦合、长度相等,存在多处相同问题。4.差分等长拱起处间距要在一倍间距到两倍间距之间。差分没有做对内等长差分走线不耦合需要加宽的走线宽度不一致多处存在开路过

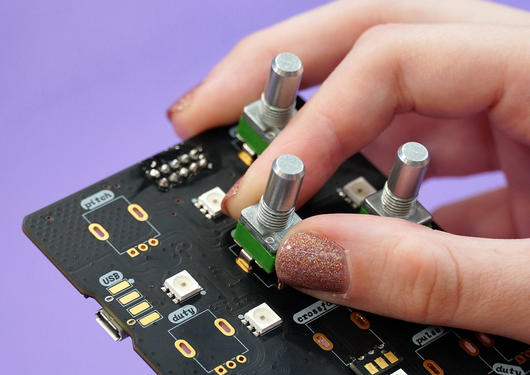

差分信号连接到过孔没有保证耦合:走线注意中心跟中心连接,注意走线规范:焊盘内走线宽度最多与焊盘同宽,拉出焊盘之后再去加粗走线:扇孔注意对齐调整:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课

工程师在进行PCB布局布线时,经常会遇见走线由于空间限制不得不“变粗/变细”,众所周知,走线宽度会引起阻抗变化,产生反射现象,对信号产生影响,所以什么情况下可以忽略这一影响?一般来说,走线宽度发生变化基本上有三大因素:阻抗变化的大小、信号上

1.注意差分走线要满足差分间距规则这个电源尽量在电源层处理,增大走线宽度线尽量走直线,不勾等长的在后边进绕蛇形电容靠近管脚摆放,一个管脚一个以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联

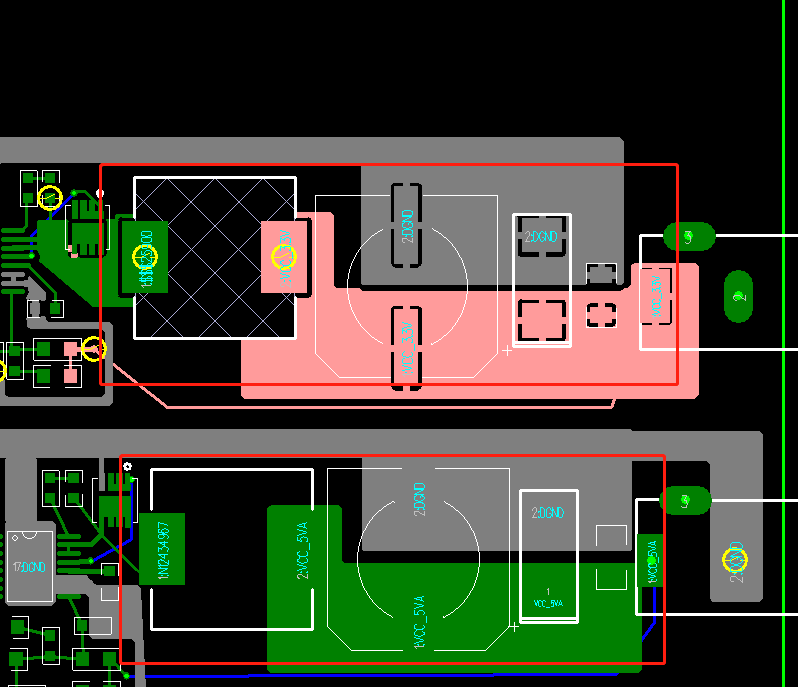

注意电源输出部分的器件整体按照中心对齐放置:器件布局注意整体的中心对齐性,调整下:此处焊盘扇孔走到其他焊盘上了:此处地直接铺铜连接上,同网络的焊盘不能直接从中间拉出连接:信号走线宽度不要随意改变:焊盘出线注意不能直接从中心拉出,要从焊盘左右

在PCB布局布线过程中,工程师经常面临着走线宽度变化的问题,由于布线空间的限制,可能会使用更新或更粗的线条来通过某些区域,但这种变化会导致阻抗不匹配,最终信号反射,对整体电路产生负面影响,因此会有哪些问题?一般来说,走线宽度会导致阻抗不匹配

扫码关注

扫码关注