- 全部

- 默认排序

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC检查时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络表的生成。忽略ERC检查点本身不具有任何的电气特性,主要用于检查原理图

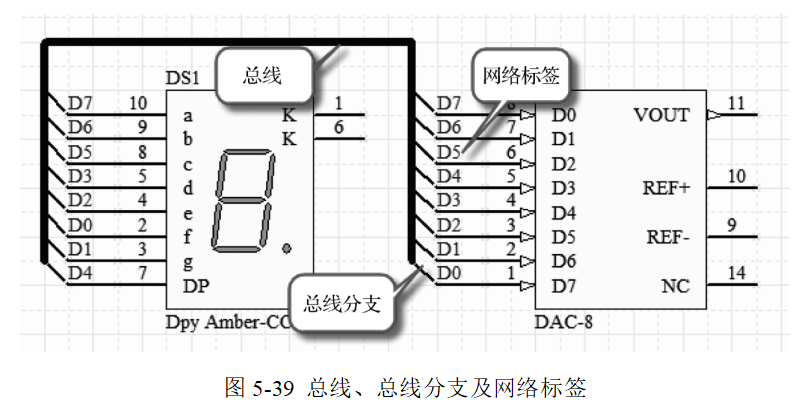

单纯的网络标签虽然可以表示图纸中相连的导线,但是由于连接位置的随意性,给工程人员分析图纸、查找相同的网络标签带来一定的困难。总线代表的是具有相同电气特性的一组导线,在具有相同电气特性的导线数目较多的情况下,可采用总线的方式,以方便识图。总线

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络报表的生成。忽略ERC检查点本身并不具有任何的电气特性,主要用于检查原理图。 图5-50 放置No E

总线由总线,总线分支及网络标号组成,代表具有相同电气特性的一组导线,在具有相同电气特性的导线数目较多的情况下,可采用总线的方式,以方便识图,这里就讲解下如何放置总线及总线分支。

Altium Designer原理图电气连接的放置— 绘制导线及导线属性设置导线是用来连接电气元件、具有电气特性的连线。1.绘制导线(1)执行菜单命令“放置-线”,如图5-30中左图所示,或者也可以按快捷键“B,激活放置导线命令,使鼠标光标

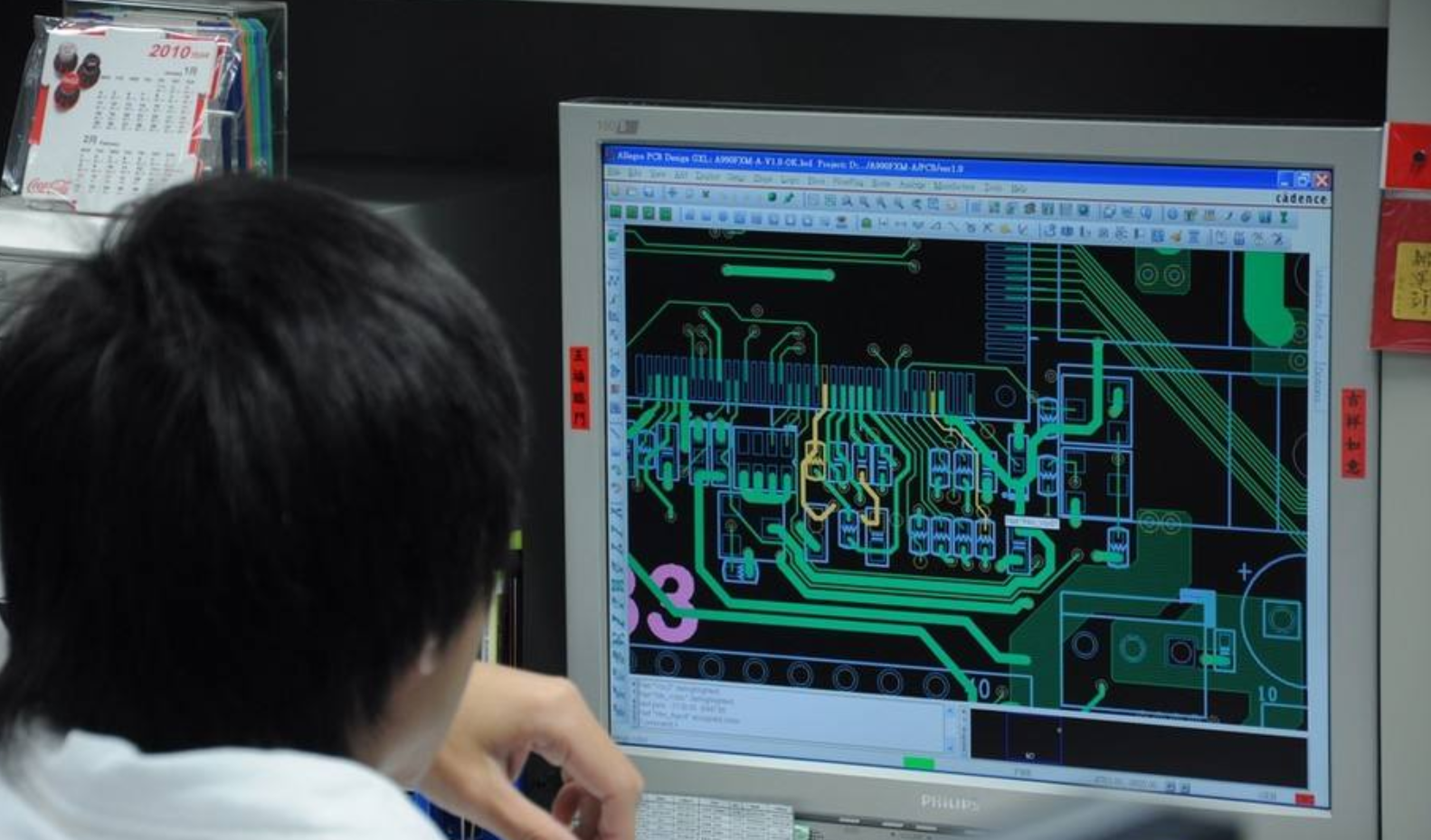

现在越来越多的高速设计是采用一种有利于加快开发周期的更有效的方法。先是建立一套满足设计性能指标的物理设计规择,通过这些规则来限制PCB布局布线。在器件安装之前,先进行仿真设计。在这种虚拟测试中,设计者可以对比设计指标来评估性能。而这些关键的前提因素是要建立一套针对性能指标的物理设计规则,而规则的基础又是建立在基于模型的仿真分析和准确预测电气特性之上的,所以不同阶段的仿真分析显得非常重要。

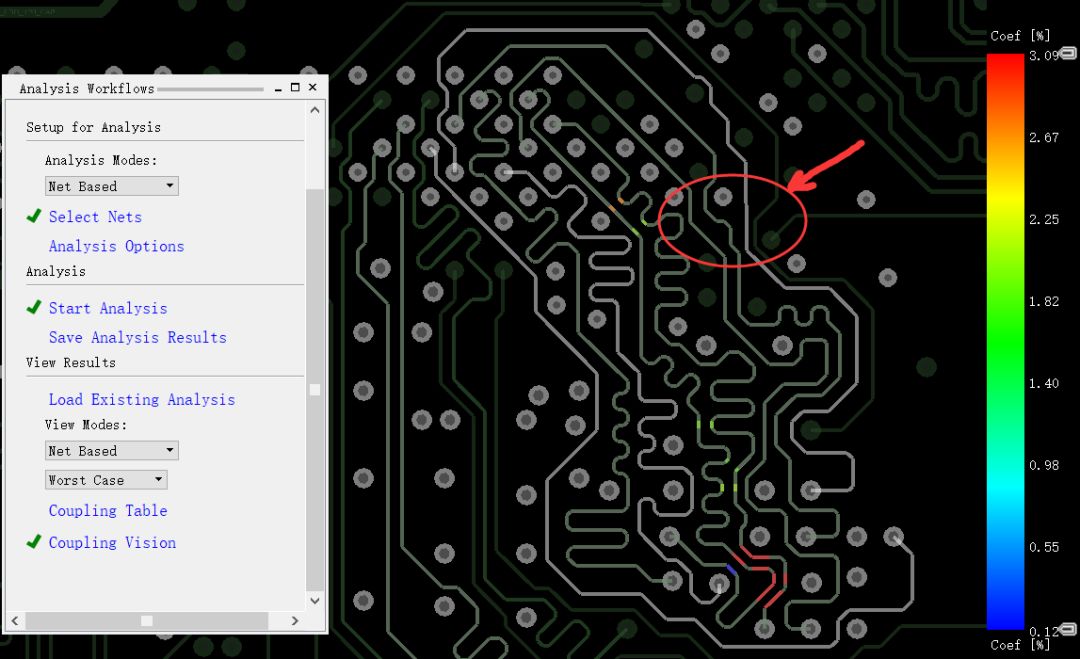

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

一、LED驱动模块RSC6218AREASUNOS(瑞森半导体)通过持续投入研发,提升LLC应用技术,集成控制芯片与功率转换,成功推出新一代产品RSC6218A WSOP-16,延续瑞森LLC拓扑方案,时机趋势完全迎合我国双碳政策,电气特性

在PCB设计、制造和装配过程中,为确保产品性能和质量,电子工程师必须进行电气特性和物理特性检查,然而对很多新人来说如何高效进行检查是个难题,所以下面将分别探讨这些检查时需要考虑的问题。1、PCB电气特性检查项目①导线参数分析:是否对导线的电

扫码关注

扫码关注