- 全部

- 默认排序

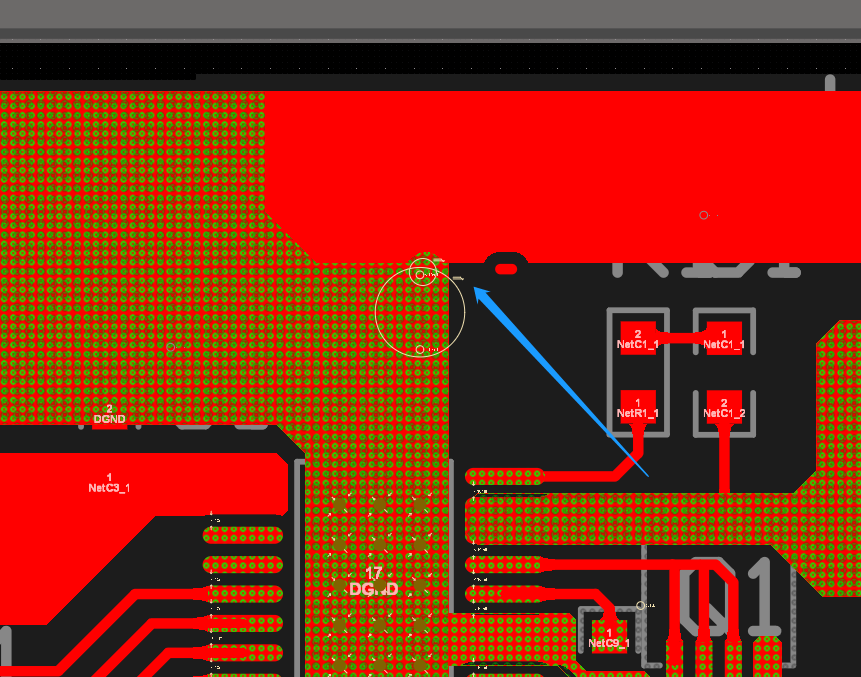

还存在开路报错,自己检查修改下:电感当前层的内部注意放置挖空区域:注意主干道器件需要整体中心对齐,都没 对齐:根据电流输出方向,电容按照先大后小的顺序布局,布局有问题:器件丝印位号没有放置整齐,要不在板外,要不就丝印重叠或者丝印覆盖焊盘了,

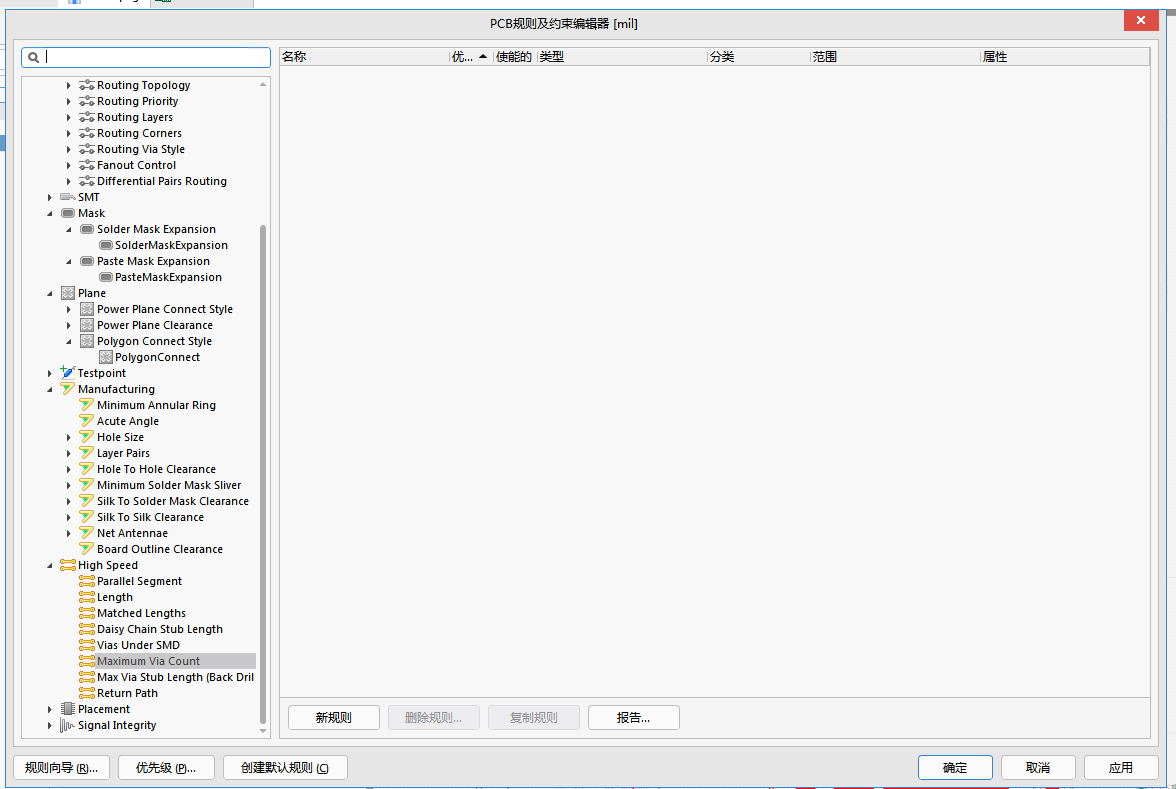

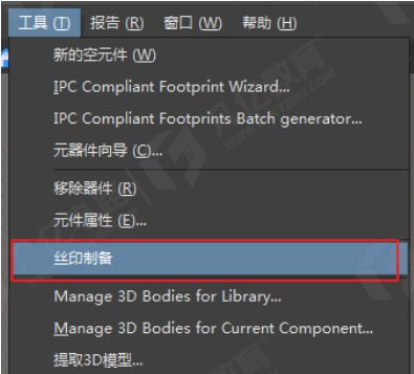

进行PCB设计时需要养成良好的设计习惯,才能保证后期的生产效果。例如整板上需要保证丝印跟阻焊的间距规则避免产生丝印重叠造成的PCB制造设计(DFM)问题。丝印重叠阻焊的影响有如下:1)PCB板后期打样,一般是以阻焊层优先,如果丝印跟焊盘重叠

在我们PCB设计的时候,有时候总会碰到丝印会重叠在焊盘上面,那么我们设置一个丝印焊盘的距离的报错就行了。如果我们丝印一附在焊盘上便会自动的报错,就是提高我们的PCB设计效率

扫码关注

扫码关注