- 全部

- 默认排序

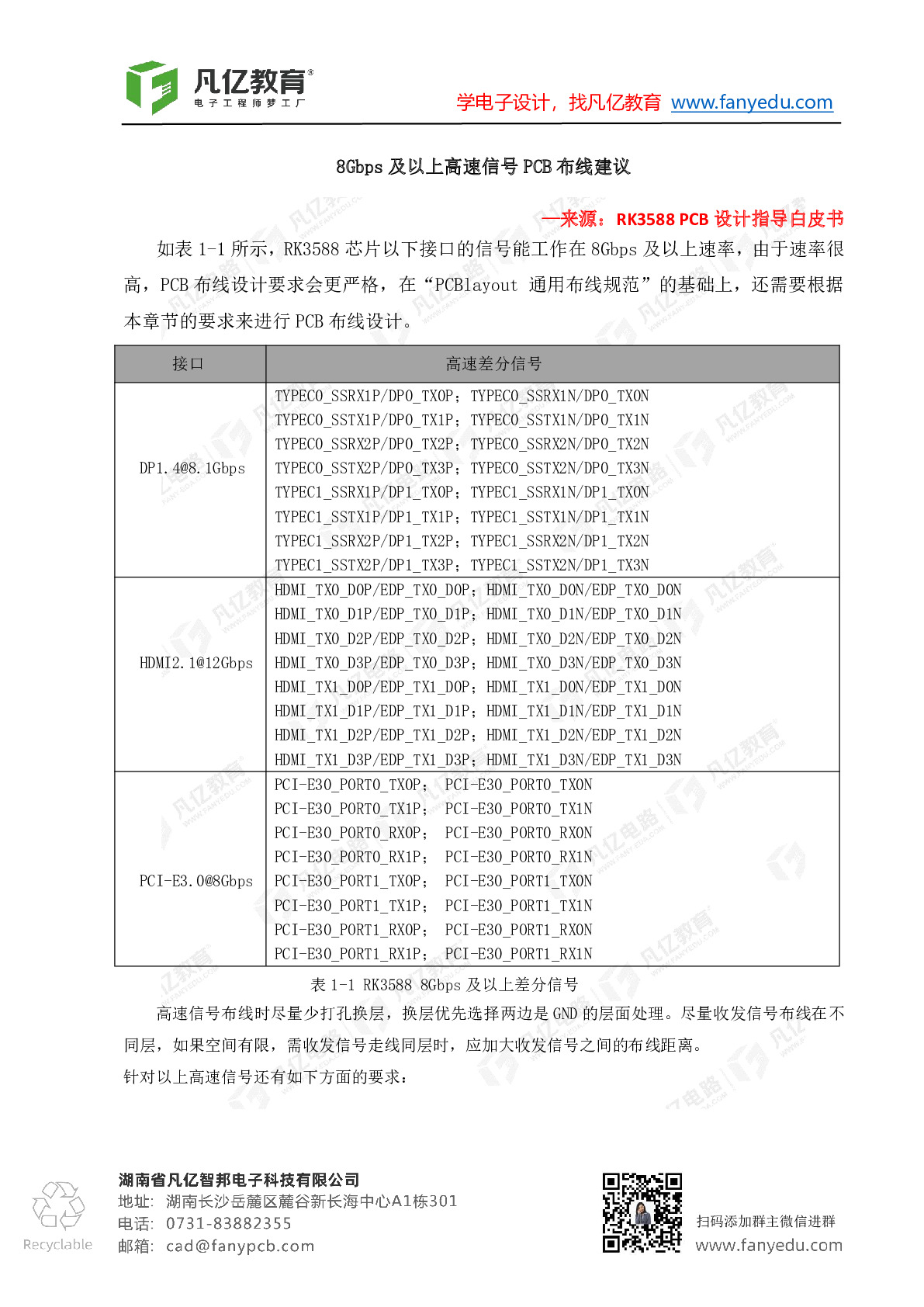

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

我们看到跟随电子设计速度越高越高,体积越来越小,功率越来越高,工程师所面临的问题越来越多,也越复杂和多样。这就要求工程师能够掌握好Cadence Sigrity2019 /Clarity/ Celsius等分析工具的使用技巧,能够在整个设计过程中解决高速问题。将这种方法让设计不用在设计过程的后期进行耗时的仿真-修复-仿真的迭代。让工程师通过以制造容限来建立拓扑和模型进行分析从而使得产品的电汽性能最优化以及成本最小化。用综合的设计和仿真分析方法来应对解决突出的技术难题。

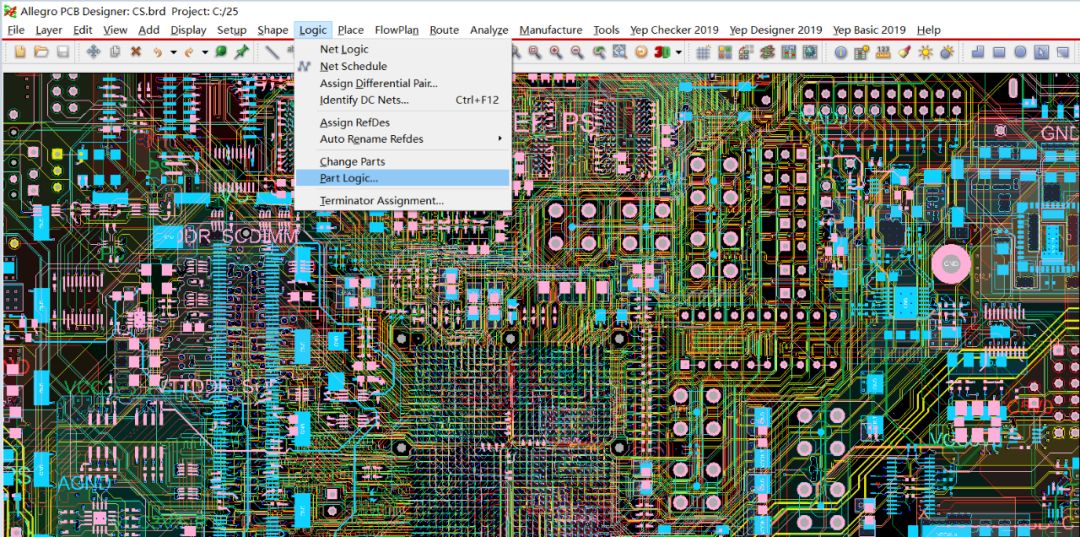

答:我们对于高速信号传输,比如差分信号、一组总线传输,都需要对其进行时序等长处理,在16.6版本以上,Allegro软件推出了自动等长的功能,在空间足够的情况下,是可以采用自动等长的功能,省去手动绕等长的时间,具体操作步骤如下所示:

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

复制这段话到TaoBao打开即可见↓4.0 hi:/信O3t7XoWNUQP信 Cadence Sigrity高速信号仿真视频实战PCB仿真教程基础套餐 凡亿扫码添加助教小姐姐【备注:仿真基础】领取更多优惠复制这段话到TaoBao打开即可见↓4.0 hi:/信O3t7XoWNUQP信 Cadence

随着电路系统设计复杂性和集成度的大规模提高,电子系统设计所面临的的挑战不再以硬件工具为主,而是传输线的工作频率和信号完整性问题等,传统电路设计知识已无法应付,这也开始要求电子工程师必须具备高速电路设计知识,因为只有通过使用高速电路,才能实现

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

相比普通PCB设计,信号质量对高速PCB设计可以说是至关重要,关系到电路的稳定性及性能。信号质量常见问题可分为过冲、回冲、毛刺、边沿和电平等,本文将详细探讨这些问题及解决方法,希望对小伙伴们有所帮助。1、过冲和回冲过冲和回冲是高速信号在传输

高速PCB板的设计方法

直播结束后扫码添加助教领取课件背景介绍:高速PCB板的信号频率以及传输速度比一般的板子高很多,有些信号速率甚至能达到20G以上,所以我们在设计的时候需要考虑信号的完整性,抗干扰能力等等,需要结合结构工程师和硬件工程师多方面考虑布局布线。高速

扫码关注

扫码关注