- 全部

- 默认排序

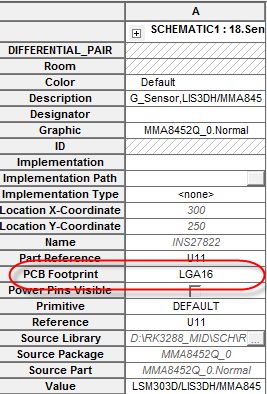

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36052): Value for property PCB Footprint contains carriage return for U11.解决的办法如下所示:第一步,错误的描述是这个器件的封装名称中含有回车键,所以在检查的时候不容易看出,需要将这个回车删除即可;第二步,找到报错的器件U11,双击这个器件,编辑器件属性,找到PCB Footprint这一栏,删除掉封装名名称后面的空格,如图3

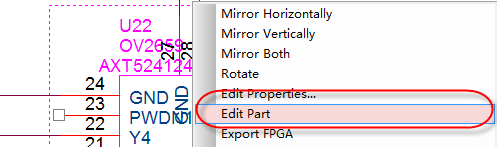

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36022): Pin number missing from Pin "1" of Package TEST , P3: SCHEMATIC1, 05.RC5T620-System Power (15.60, 8.00). All pins should be numbered.解决的办法如下所示:第一步,找到管脚缺失的器件P3,然后选中P3这个器件,点击右键,选择Edit Part属性

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36041): Duplicate Pin Name "GND" found on Package LCM0200CE1A0_3 , U22 Pin Number 25: SCHEMATIC1, 23.Camera (129.54, 50.80). Please renumber one of these.解决的办法如下所示:第一步,找到报错的器件U22,然后选中U22这个器件,点击右键,选择Edi

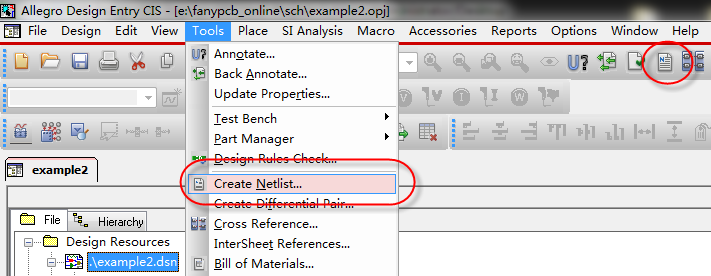

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

答:使用Orcad软件进行输出Allegro第一方网表时,弹出如图3-72所示的界面,这个是表示原理图有错误,不满足Allegro软件的要求,不能输出网表, 图3-72 输出Allegro网表报错示意图在输出Allegro第一方网表弹出这个界面,我们需要找到如图3-72所示的netlist.log这个文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的那个文件夹下,用写字本文件打开此文件,如图3-73所示,将列表中所列的错误一一解决掉,即可输出网表文件了。

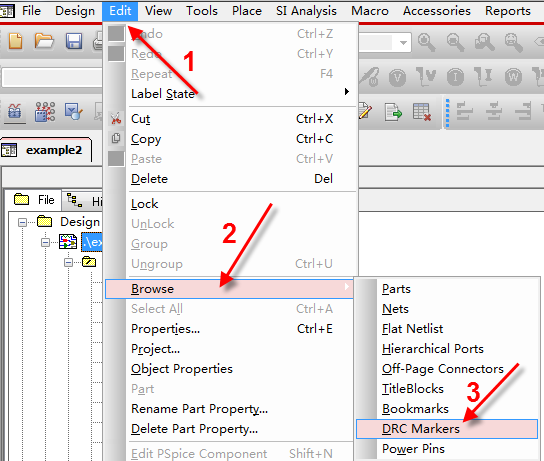

答:对原理图文件进行DRC检测以后,按照设置的DRC检测的选项,会在原理图中留下DRC的标记,对于分页的原理图来说,每一页每一页的去查看DRC的标记,比较繁琐,这里可以运用Browse功能,查看所有的DRC,操作方法如下:第一步,选中原理图的根目录,执行菜单Edit→Browse功能,然后选择DRC Marks,进行DRC标记的查看,如图3-66所示: 图3-66 浏览DRC Marks设置示意图第二步,执行命令以后,如图3-67所示,DRC ERROE显示的是错误的类型说明,DRC

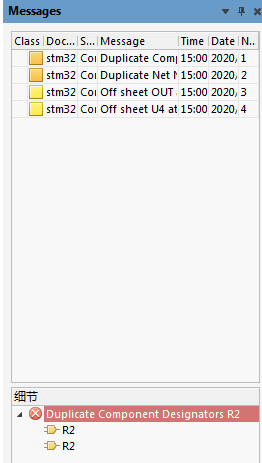

我们在编译完原理图之后有时会看见红色的波浪线,这些红色的波浪线时我们在编译后的错误显示,提示这个地方有错误。这时候我们只需要在“Messages”里面查看对应的错误类型并修改即可。

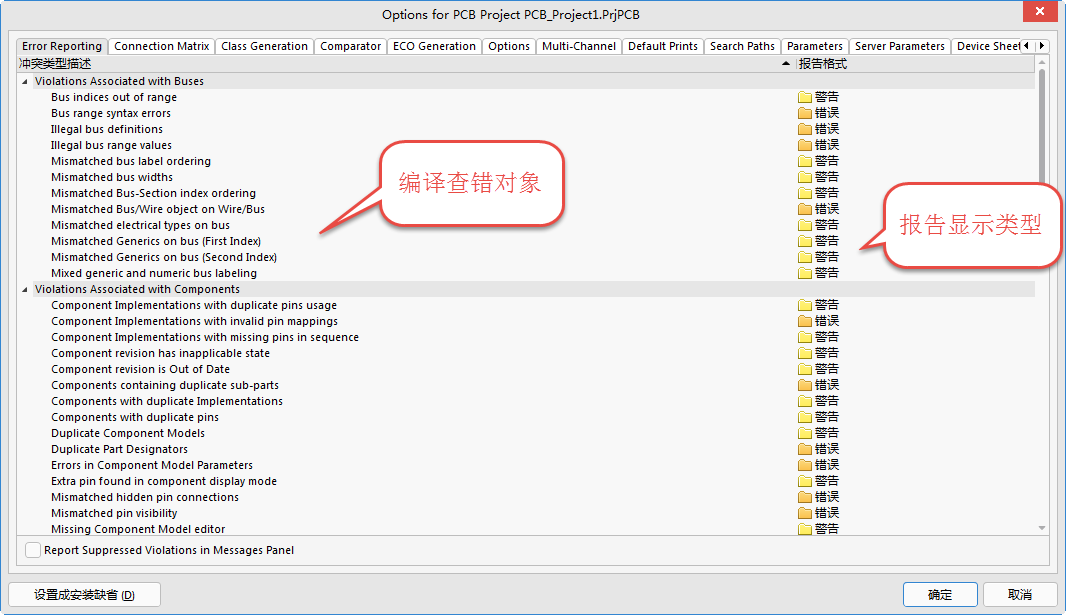

在设计完原理图之后、设计PCB之前,工程师可以利用软件自带的ERC功能对常规的一些电气性能进行检查,避免一些常规性错误和查漏补缺,以及为正确完整地导入PCB进行电路设计做准备。

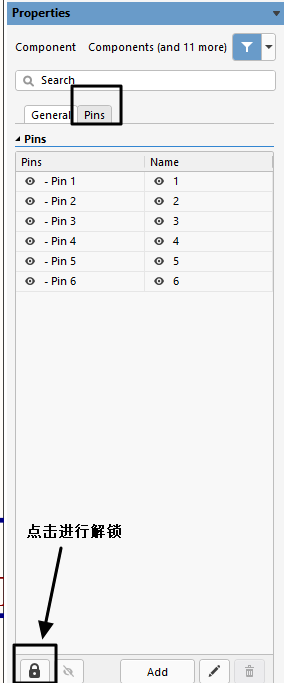

在绘制原理图时,有时会遇到元器件管脚放置错误需要更改管脚位置,或者管脚名错误需要更改管脚信息的情况,一般情况可以直接去与原理图库进行更改,这里介绍一下如何在原理图中移动元器件管脚以及更改管脚名称?

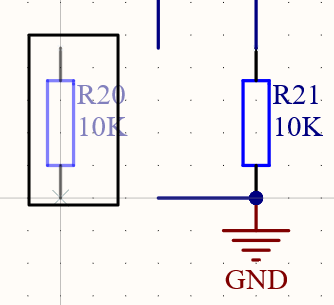

在进行原理图绘制时,经常会需要拖拽元器件,原理图中走线是默认和器件一起移动的,这样在元器件摆放错误,需要进行移动时会很不方便,那么如何使连线不和器件一器移动呢?

扫码关注

扫码关注