- 全部

- 默认排序

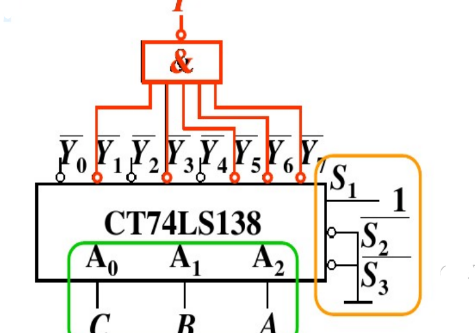

小白学习集成电路的最大难点是如何用逻辑组件来实现不同的逻辑函数,可以说是劝退许多小白的难关,为帮助小白更好地学习集成电路,今天我们将举例分享如何用译码器赫门电路实现逻辑函数,希望对小伙伴们有所帮助。需要注意的是,由于二进制译码器的输出端能提

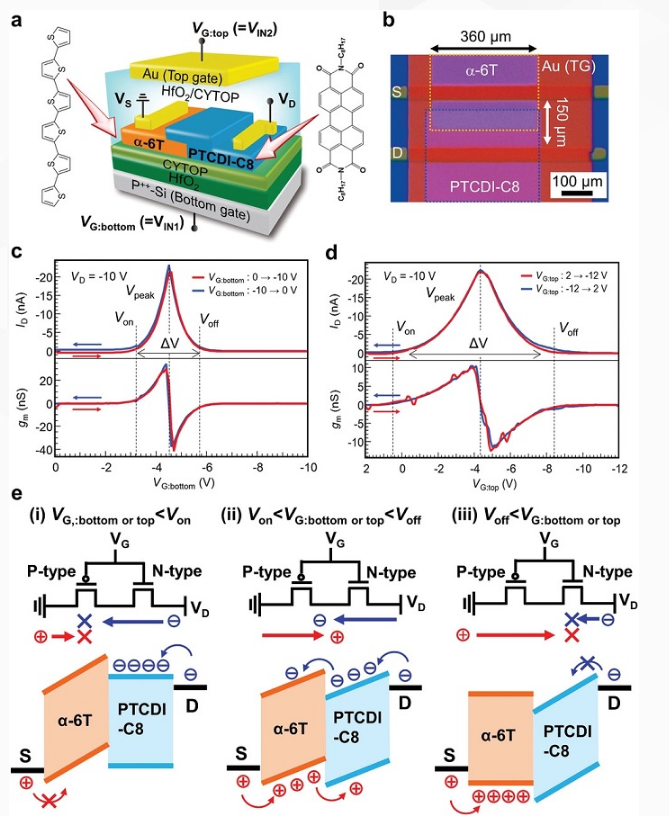

近日,来自日本国立材料研究所(NIMS)和东京理科大学的科研团队成功研发新型“有机双栅极反双级”晶体管,可通过调节执行五种逻辑门(AND、OR、NAND、NOR、XOR)操作中的任何一种双栅极的输入电压,可应用在开发“电可重构”型逻辑电路。

近日,科学组在一项概念验证研究中,成功创建能够执行简单逻辑功能的自组装蛋白质电路,该研究的成功表明:利用电子在量子尺度上的特性来创建稳定的数字电路是可行的。由于电路尺寸的减小,电路变得不可靠,这是因为创建电流所需的电子在量子尺度上表现得像波

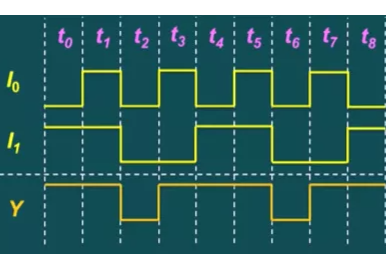

而与之对应的就是或逻辑,在数字电路中与、或、非为三大基础逻辑门电路,其后续的与非、或非、同或、异或,都是建立在基础逻辑门电路的基础上边。那么我们继续来聊基础逻辑门—或门。或门在数字电路中乃至计算机运算中的逻辑关系为加逻辑,也叫作或逻辑。而或

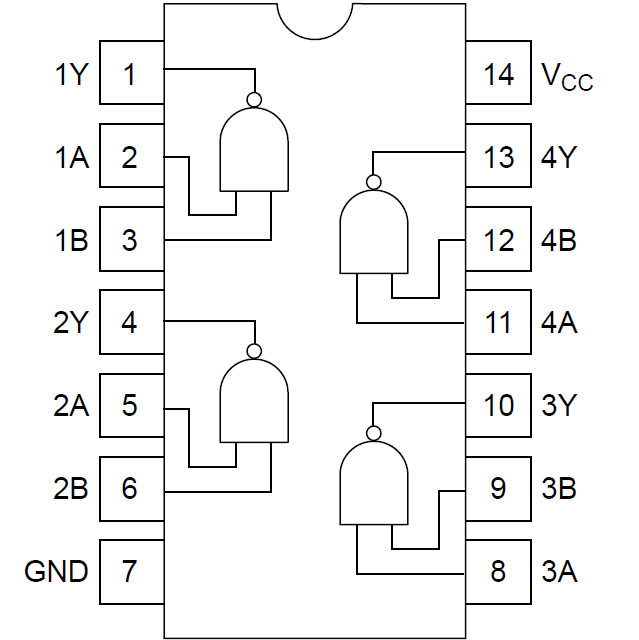

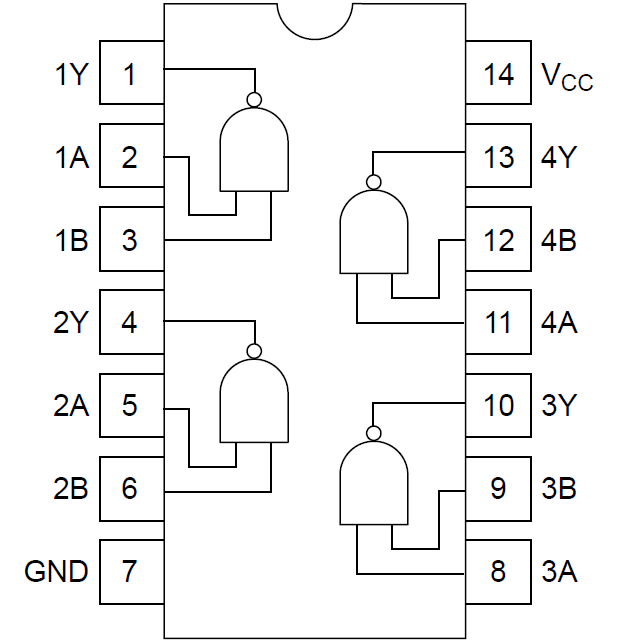

答:逻辑门电路是以简单的分立元器件组成而成,这里我们以一个简单的逻辑与非门电路74HC01为例讲解下创建方法,74HC01的逻辑电路图如图2-16所示,是由4个一样的逻辑与非门电路组合而成的。 图2-16 74HC01逻辑门示意图第一步,在olb文件单击鼠标右键,建立新的New Part,Name那一栏输入74HC01,PCB封装那一栏可以先不填写,下面的Parts per pkg输入4个,我们这个是由4个一样的与非门组成,所以做一个就可以了,然后Package Type选择

逻辑电路原理:与门逻辑电路和或门逻辑电路-若A,B,C端的高低电平分别为3V和0V。当A,B,C中有至少一个为低电平时(即0V),再加上二极管的导通压降可得,输出端F电压为0.7V,可以认为是低电平。

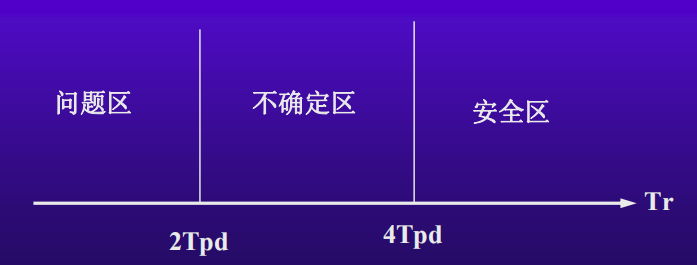

一个是从频率上来讲的含义频率高,通常认为如果数字逻辑电路设计的频率达到或超过20MH(有的说10MHz),而且工作在这个频率的电路已占整个电子系统一定的份量(常说三分之一),则称为高速电路

逻辑门电路是以简单的分立元器件组成而成,这里我们以一个简单的逻辑与非门电路74HC01为例讲解下创建方法,74HC01的逻辑电路图如图2-16所示,是由4个一样的逻辑与非门电路组合而成的。 图2-16 74HC01逻辑门示意图第一步,在olb文件单击鼠标右键,建立新的New Part,Name那一栏输入74HC01,PCB封装那一栏可以先不填写,下面的Parts per pkg输入4个,我们这个是由4个一样的与非门组成,所以做一个就可以了,然后Package Type选择Ho

数字电路中的逻辑电路

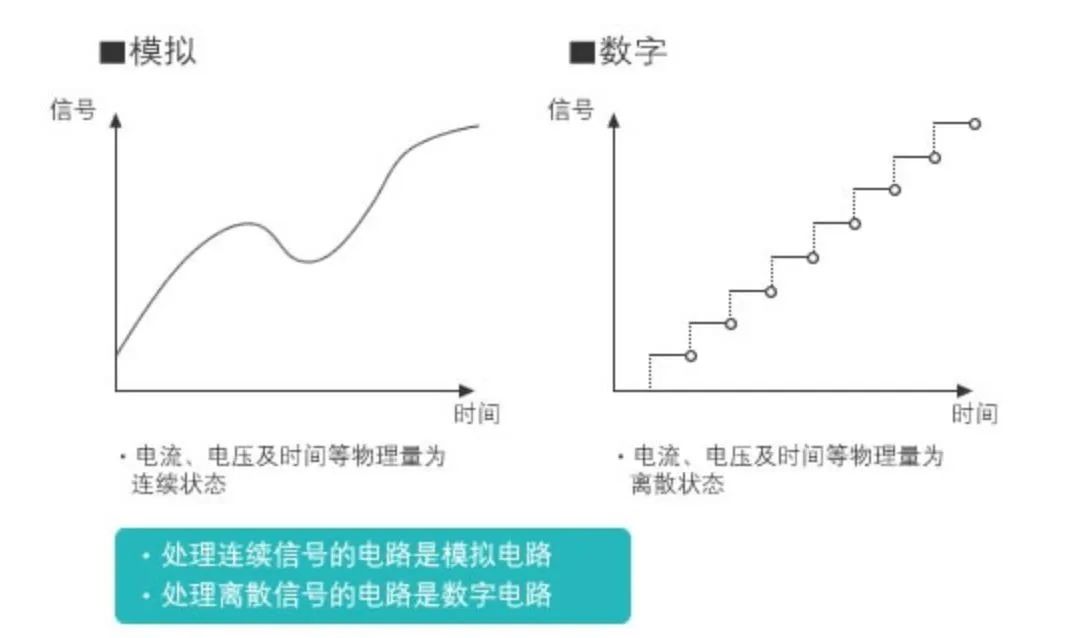

为了将自然界的模拟信息输入到象计算机那样的数字电路,需要将信息数字化(模拟信号→数字信号)。进行"模拟信号→数字信号"转换的是A/D转换器,A/D转换器按时间有规律地读取(采样)输入信号,并将其转换成用"0"和"1"表现的数值(2进制)。而整数只能表示直线上的特定点,就象是数字。于是,我们把处理连续信息的 —— 模拟信号的电路称作"模拟电路",把处理离散信息 —— 数字信号的电路称作"数字电路"。

组合逻辑电路设计,在任何特定时间只能在输入的时间取决于输出,电路的原始状态无关。“也就是说,组合逻辑电路输出电路的历史地位并不重要,电路不包括存储单元。组合逻辑表达方法有三种:真值表,逻辑表达式和电路原理图。在verilogHDL描述组合逻辑电路中,与真值表对应的是用户自定义原语;而与电路原理图相对应的是门级建模,有个绰号又叫结构化描述;与逻辑表达式相对应的则称为行为描述。

扫码关注

扫码关注