- 全部

- 默认排序

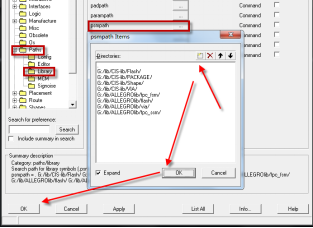

答:在将网表导入到PCB的过程中,常会由于带通孔的PCB封装内的焊盘中Flash在相应的路径中找不到,而导致导网表报错,报错内容及提示如图4-93所示: 图4-93 错误提示示意图根据图4-93所示,我们可以分析得出以下几个结论:Ø 导网表时报错的器封装名是CON2X5_2P54M。Ø PCB封装中焊盘名为PAD100SQR165THR的焊盘不能被完整提取到,原因是在设置的库路径下找不到名为THR100X165C150X180X040的Flash。对于此

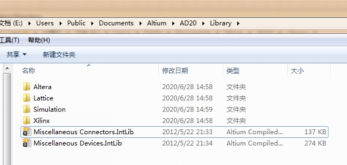

答:AD系统自带的原理图库,在我们进行设计的过程中可以直接调用,可以省去很多绘制的时间封装的时间,但是很多人不清楚他的路径在哪里?下面以AD20版本为例进行说明:路径为C:\Users\Public\Documents\Altium\AD20\Library

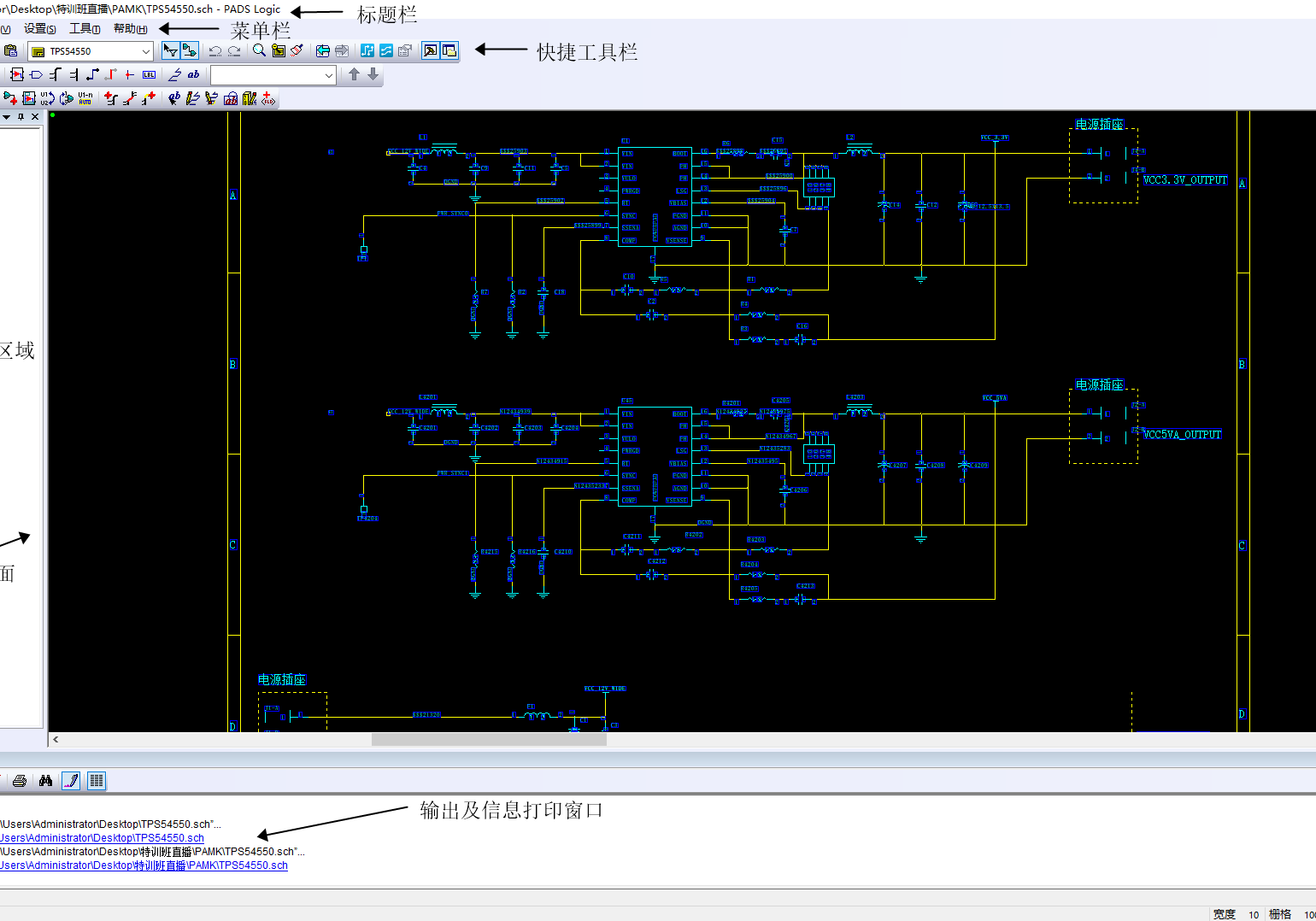

PADS Logic是PADS工具里进行原理图设计的工具。其界面由标题栏、菜单栏、快捷工具栏、项目工作界面、项目浏览器区域和输出及信息打印窗口组成,如图3-1所示。图3-1 PADS Logic工作界面Ø标题栏:显示项目的标题及路径。Ø菜单

什么是Stub 线,就是俗称的线头或歪线(特别在 Router 中经常出现), 或者说信号没打算经过的路径。通过大量的仿真和布线经验,stub会严重影响高速线的信号质量。我们在做完设计后一定要进行stub的检查和优化。

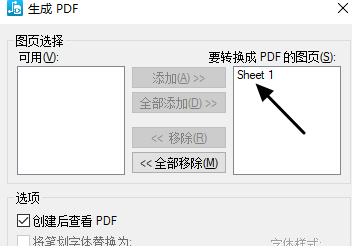

Logic设计原理图后,可以把原理图以PDF的形式输出,方便学安装软件的用户对原理图进行查阅。1)执行菜单命令“文件”→“生成PDF”进入“文件创建PDF”界面,在“文件名”栏填入文件名,指定其路径保存路径,如图4-65所示。图4-65 指

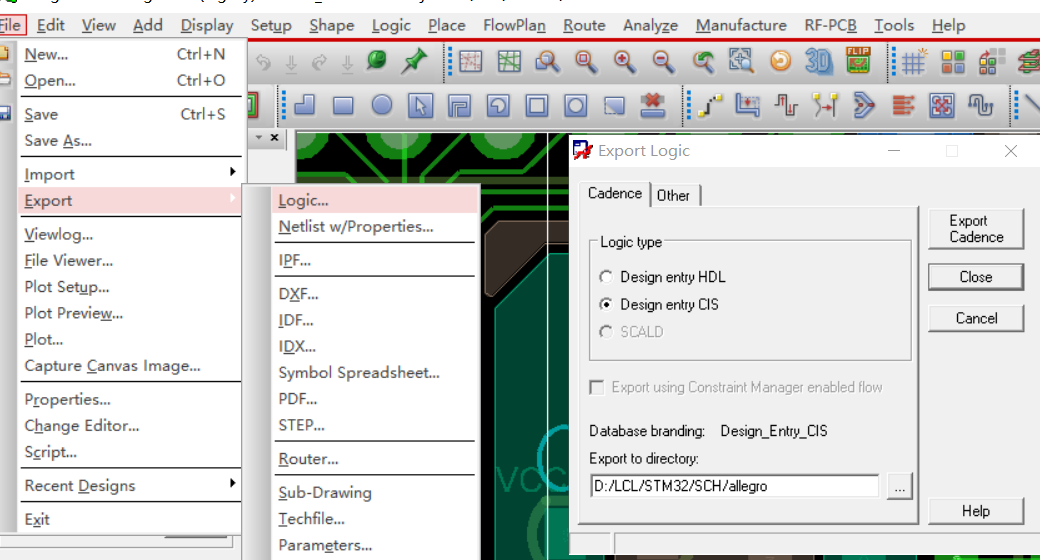

弹出export logic对话框,选择design entry CIS选项,export directory选择输出网表的路径,然后单击export directory按钮。导出完毕后,单击close按钮,关闭对话框。用orcad打开与PCB相对应的原理图,执行菜单命令tools→back annotate.....,在弹出的back annotate对话框中打开PCB editor选项卡,如图:

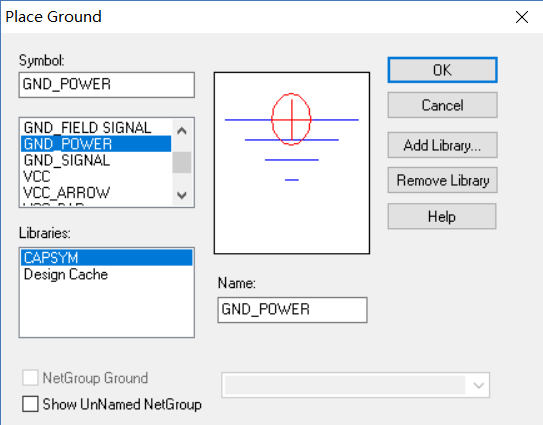

答:orcad的电源、地、分页连接符都是全局属性的,所以跟普通的元器件放置方法也不同,库的位置也不同,绘制方法在前面的问题已经有详细描述过,放置的步骤如下:第一步,点击菜单Place→Power/GND,或者是按快捷键F/G,放置电源连接/地连接,在弹出的电源/地的属性对话框中,在下面的Librarys中添加库的路径,一般电源与地可以直接调用系统的库CAPSYM.OLB,不用再重新加载新的库,在上面的Symbol列表中选择对应的符号即可,右侧的Name中输入电源与地的网络名称,如图3-15所示;

IC设计工程师必备技能

一、直播时间2022年9月24日 晚8点直播福利扫码添加助教领取二、直播介绍现如今,越来越多的年轻人立志投身芯片产业。但在向着这个目标奋斗的过程中,却很难得到现实可行的指导,对自己的职业规划和职业前景感到迷茫。本期讲座针对IC职业发展中的现实问题,希望为大家描绘一条清晰的培养和发展路径。三、直播大纲1)企业的分工2) IC企业的研发流程3) IC企业的EDA工具链4) IC设计工程师的必备技能5) IC验证工程的必备技能6) 答疑环节四、直播能帮助到用户些什么1)了解IC企业的分工和流程2)了解IC设计的EDA工具链3)了解IC设计工程师和验证工程师需要哪些必备技能4)回答用户在职业发展方面的各种疑问五、讲师介绍皮特派,厦大硕士,B站up主,从事芯片设计和算法研发十余年,先后任职于多家国内知名芯片公司以及创业团队,担任算法经理和数字开发经理。精通WiFi、射频数字校准、ADC、数模混仿等领域。拥有国家发明专利4项。

天线设计技术在物联网时代的价值;硬件工程师为什么要学会一般性板载PCB天线的开发技术;如何避开复杂的天线辐射理论,并通过具体的结构和电流路径分析方法进行PCB天线的开发;天线设计方法在高速电路开发中的引申。

扫码关注

扫码关注