- 全部

- 默认排序

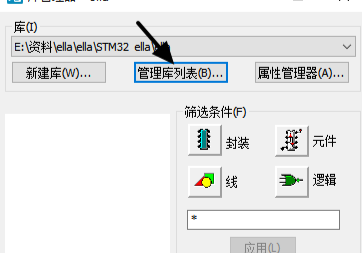

进行原理图与PCB同步导入网络表时,软件默认优先从元件库列表中的第1个库开始调用元件,所以创建元件库后,需要将使用的库移动至库列表最顶端。1)点击管理库列表按键,在弹出的对话框中选择创建的lib1库,点击“上”选项将lib1移动到顶端后点击

我的是ad15,在做网络报表时只有如图四个选项卡,求高手指导(我装了ad19之后是有protel选项的,另外我ad14,15都试了,这两个版本都没有)

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC检查时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络表的生成。忽略ERC检查点本身不具有任何的电气特性,主要用于检查原理图

请问这种错误要怎么解决,按工具里的复位错误标志可以取消,但在最后检查时还是会报错,来回导入好几次都是这样,怎么解决,求解答

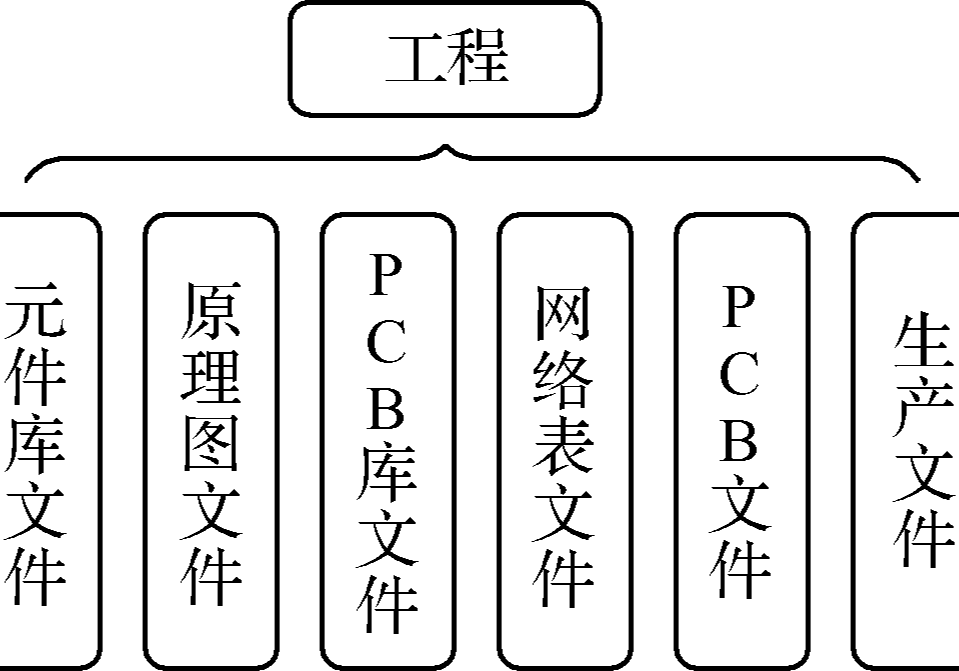

一个完整的PCB工程应该包含哪些内容?新一代Altium Designer集成了相当强大的开发管理环境,能够有效地对设计的各种文件进行分类及层次管理。本章通过图文的形式介绍工程的组成及完整工程的创建,有利于读者形成系统的文件管理概念。熟悉A

硬件高手的网表妙招

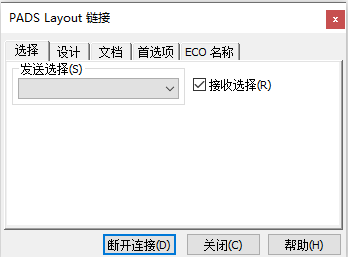

网表也称网络表,顾名思义,就是网络连接和联系的表示,其内容主要是电路图中各个元件类型、封装信息、连接流水序号等数据信息。在使用Altium Designer进行PCB设计时,可以通过导入网络连接关系进行PCB的导入。当今几大主流PCB设计软件都支持Altium Designer格式网表导出,这也极大地提高了Altium Designer对其他类设计软件的兼容性,如图8-10所示。

穿插讲述了Cadence17.4原理图工具的使用方法和GD32E230硬件设计外围电路配置方法,各种常用芯片的使用等内容。力增用一个从无到有的设计方式,从原理图的设计构思开始,通过视频的方式带领大家从原理图设计到错误检查,网络表生产,封装库制作,同步进入PCB,3D模型制作,布局,规则,布线,文件输出的操作全流程和设计方法等经典操作。

扫码关注

扫码关注