- 全部

- 默认排序

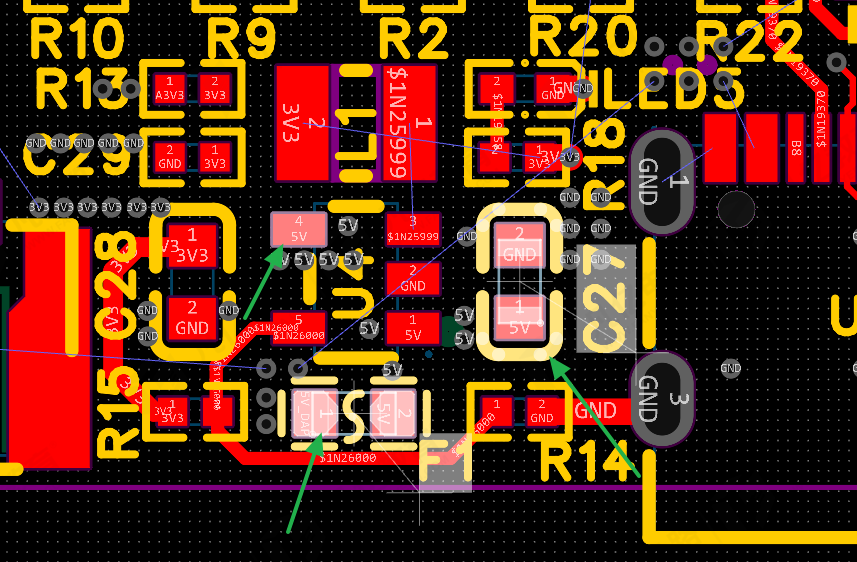

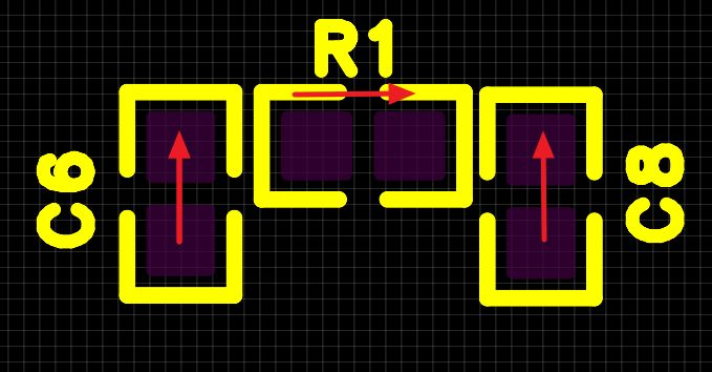

时钟信号包地需要在地线上间隔150mil-200mil打上一个地过孔2.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.器件摆放注意对齐处理4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊;地网络打一个孔即可,

在PCB设计中,多种多样的选择是怎么实现的呢?下面介绍选择的方法。1、单选单击鼠标左键可以进行单个选择。2、多选(1)按住“ctrl”,多次点击鼠标左键,进行选择。(2)从左上角按住鼠标左键,向右下角拖动鼠标,在框选范围内的对象都会被选中,

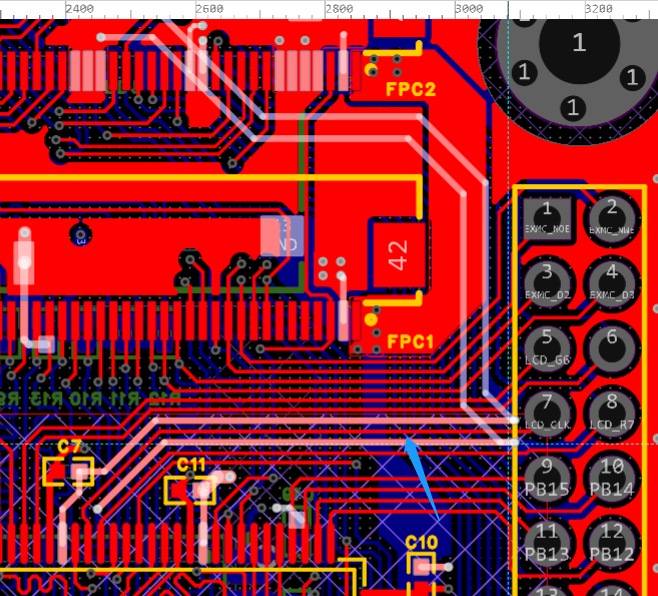

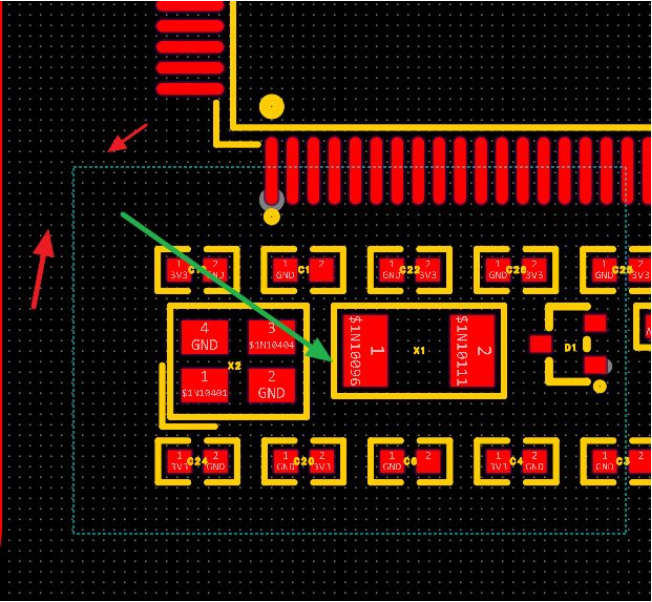

电源输入电容应该靠近管脚放置输出电容电阻应该靠近管脚放置到电感后面输出3.3v晶振布局错误,晶振的一对线要走成类差分的形式, 线尽量短如下图。typec的LCD_R4、LCD_R5要走差分阻抗控制90欧姆做对内等长,差分走线尽量减少打孔换层

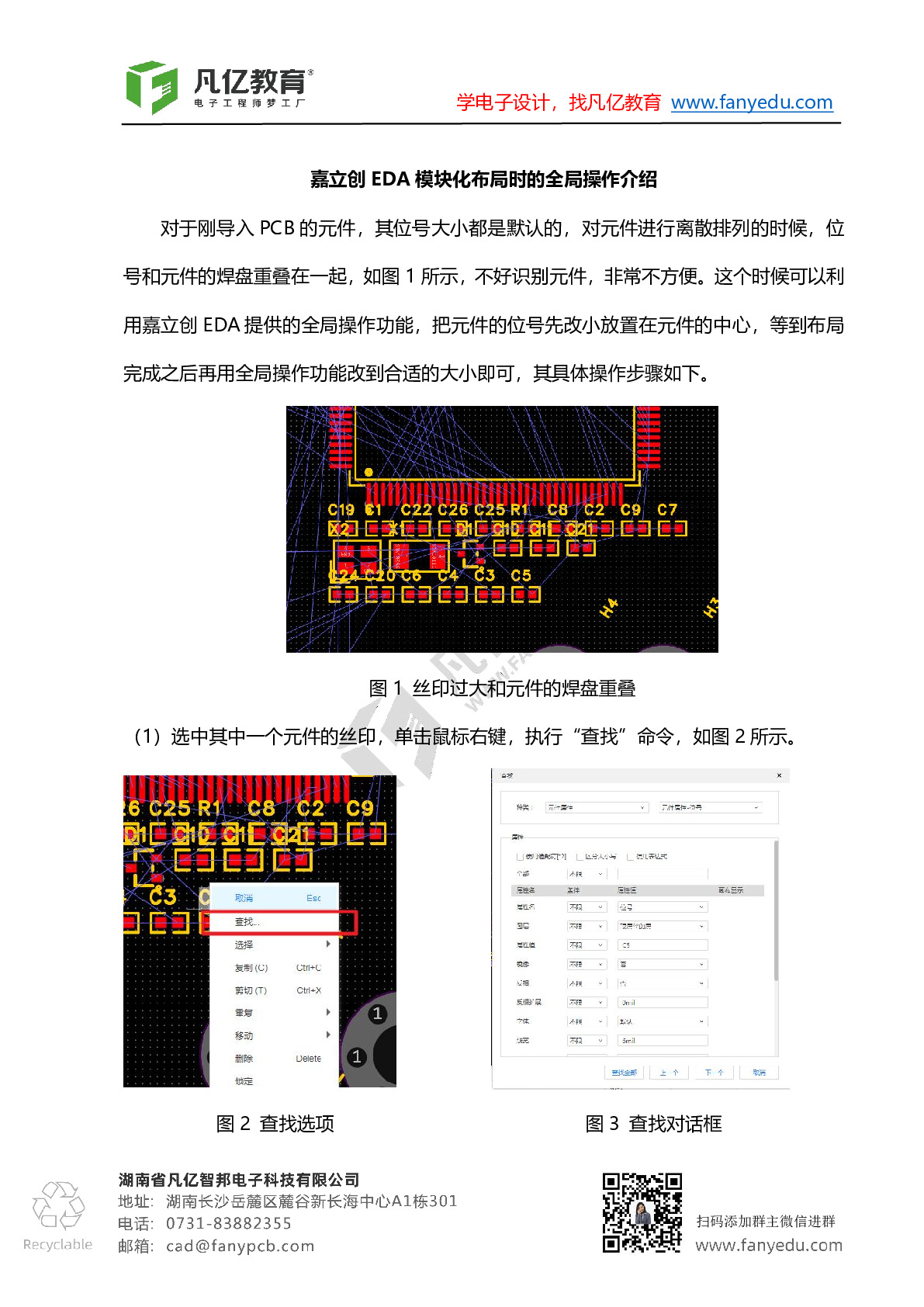

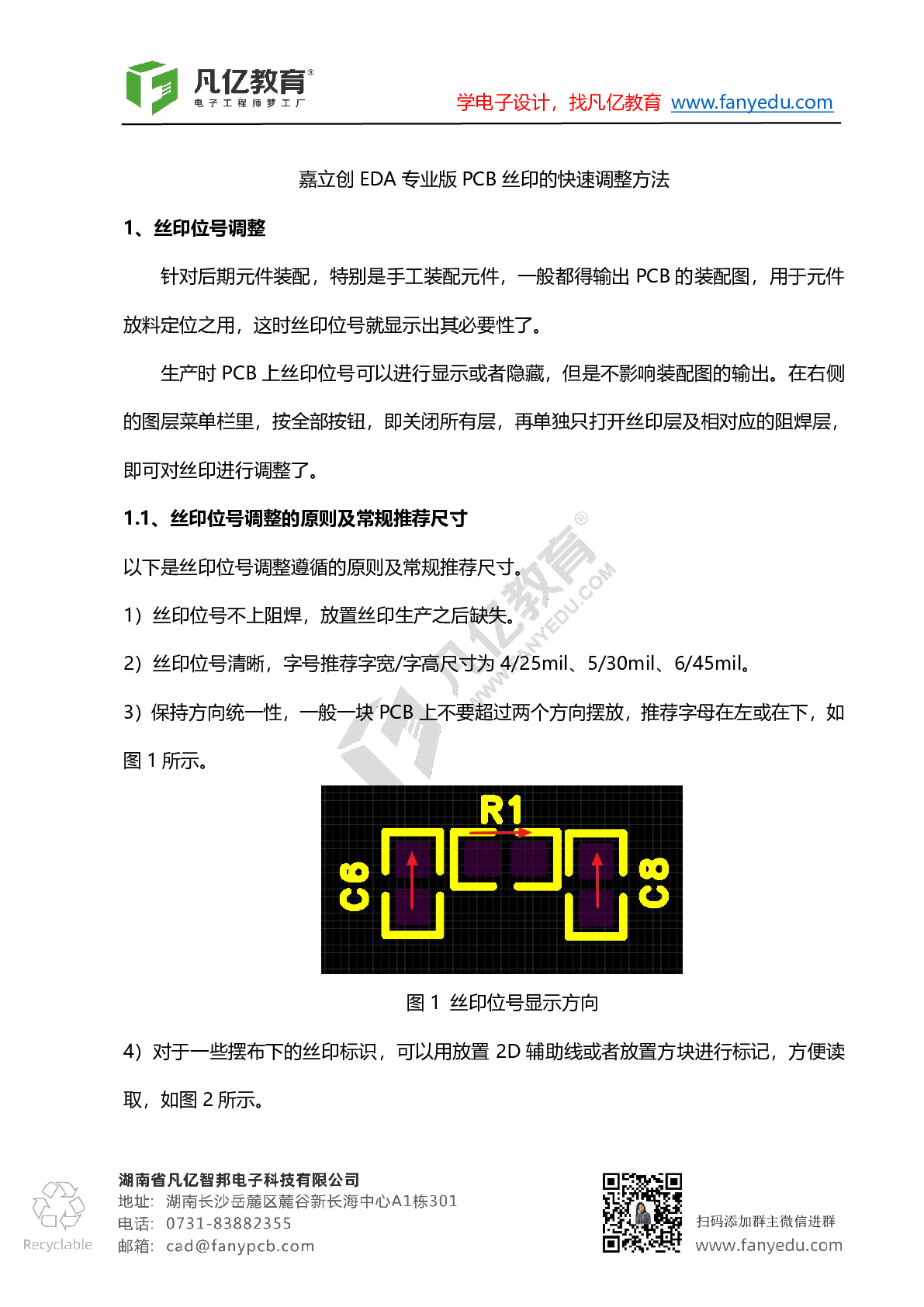

一、丝印位号调整针对后期元件装配,特别是手工装配元件,一般都得输出PCB的装配图,用于元件放料定位之用,这时丝印位号就显示出其必要性了。生产时PCB上丝印位号可以进行显示或者隐藏,但是不影响装配图的输出。在右侧的图层菜单栏里,按全部按钮,即

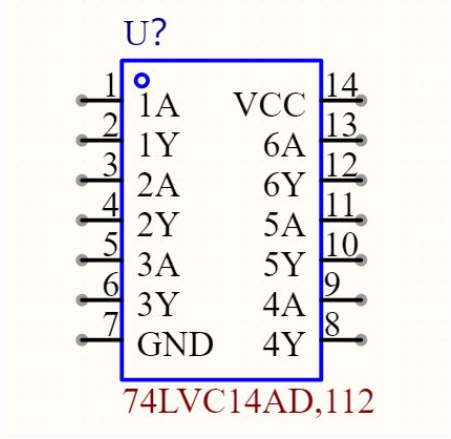

一、元件符号概述如图1所示,元件符号是元件在原理图中的表现形式,主要由元件边框、管脚(包括管脚符号和管脚名称)、元件名称及说明组成,通过放置的管脚来建立电气连接关系。元件符号中管脚序号是和电子元件实物的管脚一一对应的。在创建元件的时候,图形

近日,EDA大厂新思科技(Synopsys)因涉嫌向华为海思和中芯国际提供帮助,而被美国商务部调查。引发了许多争议,虽然是关于美国制裁的老生常谈话题,但这也侧面反映我国EDA软件方面的弱势。会EDA软件?能电路设计?懂电路理论?>>《弟子计

电源模块反馈电路错误,r15接入反馈电源到r14在到5号管脚。2.晶振布局布线错误3.typec差分对内误差控制5mil以内,尽量避免出现不耦合4.TF卡所有信号线要整组 ,做等长处理以时钟线为目标,目标控制在300mil以内。

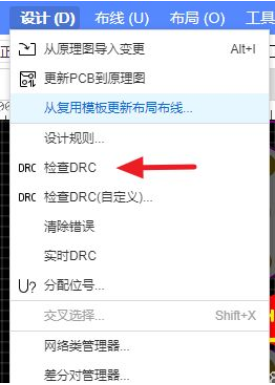

前期为了满足各项设计的要求,通常会设置很多约束规则,当一个PCB设计完成之后,通常要进行DRC。DRC就是检查设计是否满足所设置的规则。一个完整的PCB设计必须经过各项连接性规则检查,常见的检查包括开路及短路的检查,更加严格的还有差分对、阻

扫码关注

扫码关注