- 全部

- 默认排序

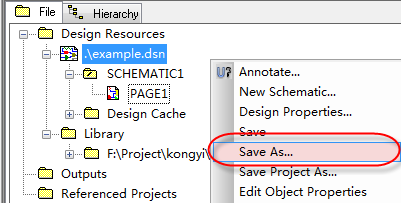

答:我们在进行原理图设计或者是进行PCB设计,都会遇到这样的问题,需要降低设计文件的版本,我们这里讲解下,Orcad软件设计的原理图如何去降低原理图的版本,操作的步骤很简单,我们这里列举一下操作的步骤:第一步,需要选中降低原理图的根目录就是DSN文件,如图3-212所示,选中之后,点击鼠标右键,Save As,就可以存为低的版本; 图3-212 原理图另存低版本示意图第二步,在弹出的界面中,如图3-213所示,在保存类型那一栏可以选择低的版本,一般是存为16.2的版本,这样就存为了低的

课程目录大纲一 51 单片机介绍1. 单片机的组成2. 单片机最小系统3. 单片机核心板4. 开发工具准备二 51 集成开发环境1. Keil 平台搭建2. 设置颜色、字体、文本编码3. 设置输出固件格式三 51 新建工程模板1. Keil

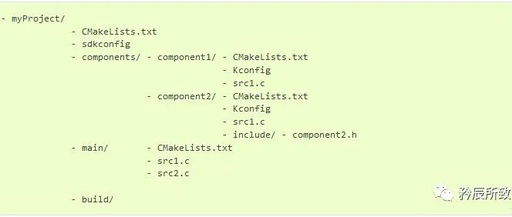

ESP32-C3 学习测试到今天,一直在使用 ESP-IDF 的框架,但是还从来没有注意过工程结构,遇到复杂一点的项目,工程结构就显得太乱了,本文就来了解下 ESP-IDF 工程结构。前言一、ESP-IDF工程基本框架1.1 工程主目录下的文件1.2 main目录下的文件1.3 components

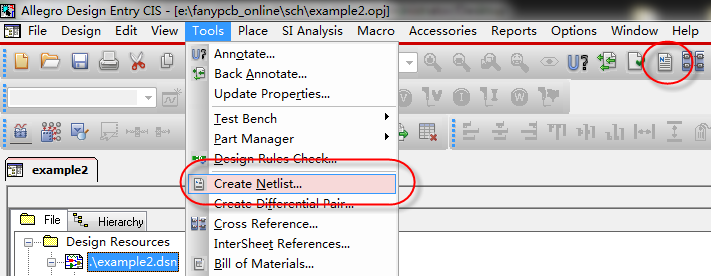

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-68所示; 图3-68 产生网表示意图第二步,弹出的Creat Netlist界面中,选择的是PCB Editor,产生Allegro的第一方网表,如图3-69所示; 图3-69 Allegro第一方网表参数设置示意图第三步,输入Allegro第一方网表需要注意下面几个

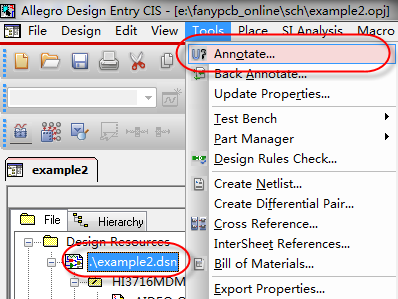

答:第一步,选中整个原理图的根目录,然后执行菜单Tools-Annotate,如图3-52所示,进行原理图选项的编辑; 图3-52 原理图编译示意图第二步,在弹出的原理图编译界面中,如图3-53所示,在Action选项中,现将原理图本身已经存在的位号全部复位,点击Reset Part References to “?”,则全部的位号则变成的问号,如图3-54所示; 图3-53 原理图编译界面设置示意图 图3-54 原理图所有位号复

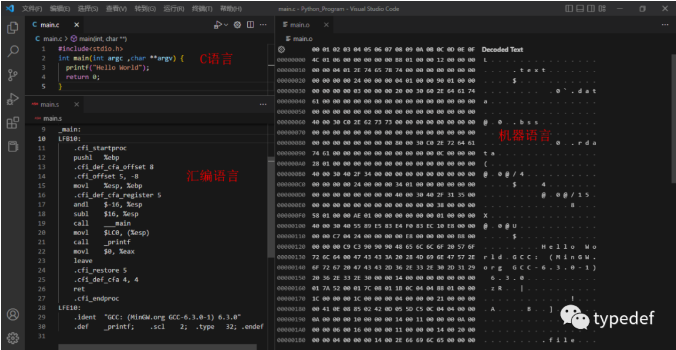

目录:简述C语言由来BCPL语言及代码B语言以及代码C语言编程语言机器语言汇编语言高级语言C为何快速1. 简述都说C语言编写的程序执行效率比较高,那么到底高在哪里,我们一块来学习学习。2. C语言由来C语言源自于BCPL、B两种语言。BCP

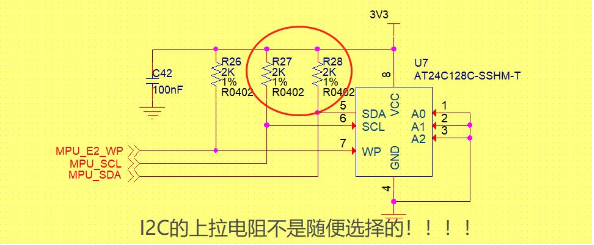

相信很多人都清楚,在I2C总线上需要接上拉电阻?但是您针对对I2C上拉电阻足够了解吗?本文带您详细掌握一下I2C的上拉电阻。目录如下:上拉电阻的含义、上拉电阻在 I2C 电路中的作用根据VOL和IOL计算I2C上拉电阻的最小值根据总线电容计

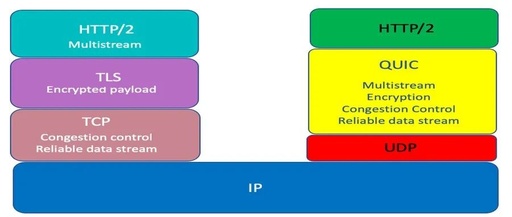

文章目录一、QUIC 如何解决TCP的队头阻塞问题?1.1 TCP 为何会有队头阻塞问题1.2 QUIC 如何解决队头阻塞问题1.3 QUIC 没有队头阻塞的多路复用二、QUIC 如何优化TCP 的连接管理机制?2.1 TCP连接的本质是什么2.2 QUIC 如何减少TCP 建立连接的开销2.3 Q

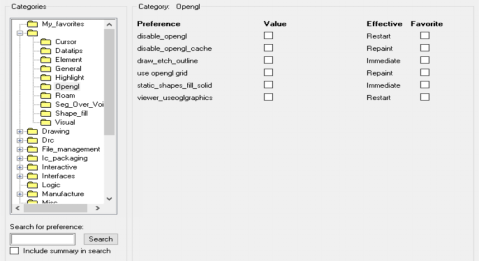

答:第一步,点击执行菜单命令Setup-User prefeences,进行用户设计属性的设置;第二步,执行命令之后,弹出如图5-229所示的界面,左侧边栏为常规设计参数的根目录,右侧边栏为常规设计参数的设置选项,具体的含义如下所示:

扫码关注

扫码关注