- 全部

- 默认排序

一、输入失调电压(Offset Voltage,VOS) (一)定义:在运放开环使用时, 加载在两个输入端之间的直流电压使得放大器直流输出电压为 0。 (二)优劣范围:1µV 以下,属于极优秀的。100µV 以下的属于较好的。最大的有几十mV。 (三)对策: 1)选择 VOS远小于被测直流量的放大器, 2)过运放的调零措施消除这个影响 3)如果你仅关心被测信号中的交变成分,你可以在输入端和输出端增加交流耦合电路,将其消除。 4)如果 IB1=IB2,那么选择 R1=R2//RF,可

1.Altium Designer将需要做等长的线组成一个类:在Design-Classes中,右键Net Classes弹出菜单中,选择Add Class,为新New Class命名(Rename Class),加入需要的Net。

物联网嵌入式培训课程

相信有很多同学对于物联网只是有所耳闻,只是知道未来我们将处于物联网时代,但对物联网嵌入式培训却不太了解。那物联网嵌入式培训都要学习哪些内容呢?今天小编就将带领我们进入物联网嵌入式培训的世界。 何为物联网(IoT, internet of things)?从物联网学习的角度来说,物联网是在嵌入式的传统培训模式或者学习道路上,增加了一些互联互通,加了无线传输(ZigBee、BLE、Wi-Fi等),加了传感器,加了射频识别(各种频段RFID)。像现在非常火的NB-IOT/LoRA,就是物联网比较典型

2020年1月5日下午1点半,由21ic中国电子网举办的深圳线下网友技术分享沙龙在深圳市戴言有趣咖啡厅顺利进行。 参加本次活动的有21ic电子网论坛的高磊亮老师、林杰老师、马佳老师、黄勇老师等共7名资深版主、员工以及电子硬件爱好者。其中,黄勇老师代表凡亿教育作为特邀嘉宾参加了此次技术分享交流会。 黄勇老师作为凡亿教育的创始人,长期致力于Cadence Allegro高速PCB设计与Cadence Allegro高速PCB设计视频教学;具备丰富的PCB设计实战经验,尤其擅长高速信号数字类、消费

器件寿终正寝的原因

器件的"寿终正寝"是一种源于物理或化学变化的累积性衰退效应。大家都知道,电解电容和某些类型的薄膜电容"终有一死",原因是在微量杂质(氧气等)和电压力的共同作用下,其电介质会发生化学反应。集成电路结构遵循摩尔定律,变得越来越小,正常工作温度下的掺杂物迁移导致器件在数十年(而非原来的数百年)内失效的风险在提高。另外,磁致伸缩引发的疲劳会使电感发生机械疲劳,这是一种广为人知的效应。某些类型的电阻材料会在空气中缓慢氧化,当空气变得更为潮湿时,氧化速度会加快。同样,没有人会期望电池永远有效。

深圳晶振电路的PCB设计

我们常把晶振比喻为数字电路的心脏,这是因为,数字电路的所有工作都离不开时钟信号,晶振直接控制着整个系统,若晶振不运作那么整个系统也就瘫痪了,所以晶振是决定了数字电路开始工作的先决条件。 我们常说的晶振,是石英晶体振荡器和石英晶体谐振器两种,他们都是利用石英晶体的压电效应制作而成。在石英晶体的两个电极上施加电场会使晶体产生机械变形,反之,如果在晶体两侧施加机械压力就会在晶体上产生电场。并且,这两种现象是可逆的。利用这种特性,在晶体的两侧施加交变电压,晶片就会产生机械振动,同时产生交变电场。这种震

许多人感觉PCBlayout的工作中是很枯燥乏味无趣的,每日冲着木板不计其数条布线,各式各样的封裝,反复着拉线的工作中。可是设计工作人员要在各种各样设计标准中间做选择,兼具特性,成本费,加工工艺等各个领域,又要留意到板子合理布局的有效齐整,并沒有看起来的这么简单,必须大量的智慧型。深圳pcb培训班说说在设计时培养一些稳定的工作习惯性,会给你的设计更有效,制造更非常容易,特性更佳。

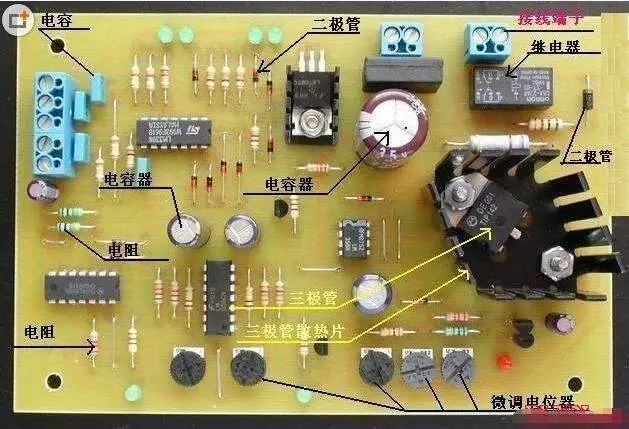

什么是集成电路设计

集成电路设计,根据当前集成电路的集成规模,亦可称之为超大规模集成电路设计,是指以集成电路、超大规模集成电路为目标的设计流程。集成电路设计通常是以“模块”作为设计的单位的。例如,对于多位全加器来说,其次级模块是一位的加法器,而加法器又是由下一级的与门、非门模块构成,与、非门最终可以分解为更低抽象级的CMOS器件。下面就让我们进一步的了解集成电路设计的相关知识。 集成电路设计介绍 集成电路设计的流程一般先要进行软硬件划分,将设计基本分为两部分:芯片硬件设计和软件协同设计。芯片硬件设计包括: 1

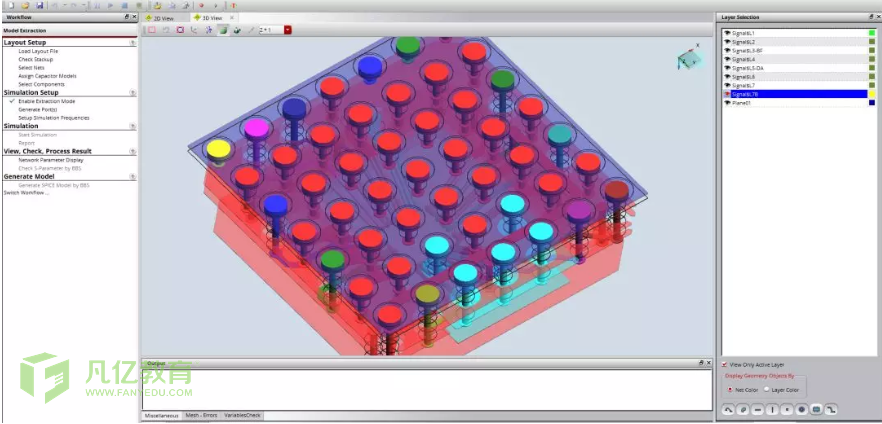

在IC封装的分析中,为了能够提取到更加趋近于真实测量结果的S参数(或者其他参数),需要在封装体上添加假性球体和参考层,下面来讲解在Sigrity™ PowerSI®工具中添加假性球体和参考层的方法。

扫码关注

扫码关注