- 全部

- 默认排序

RX TX没有设置等长组以及等长误差进行等长:注意RX TX信号可以走一根GND走线进行分隔开:其他的没什么问题了。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://

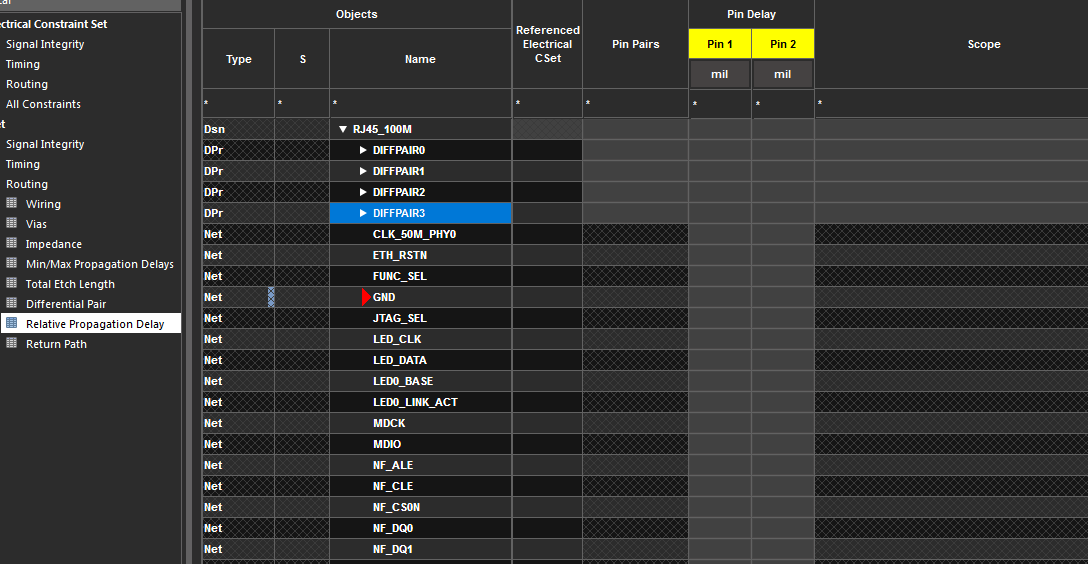

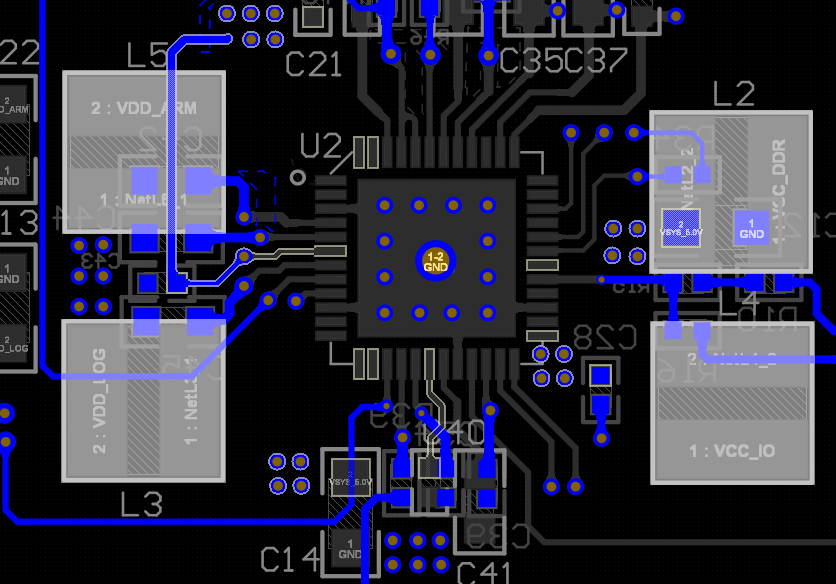

每组差分都要耦合走线,都不合格删除重新拉:先理解差分耦合走线,都不合格:差分走线间距都不一样,都要耦合:基本差分都要改,完全不合格。网口差分都是100OM,没有90:RX的走线等长还可以调整下,咬合等长即可,这样随意等长占的空间太大了:整板

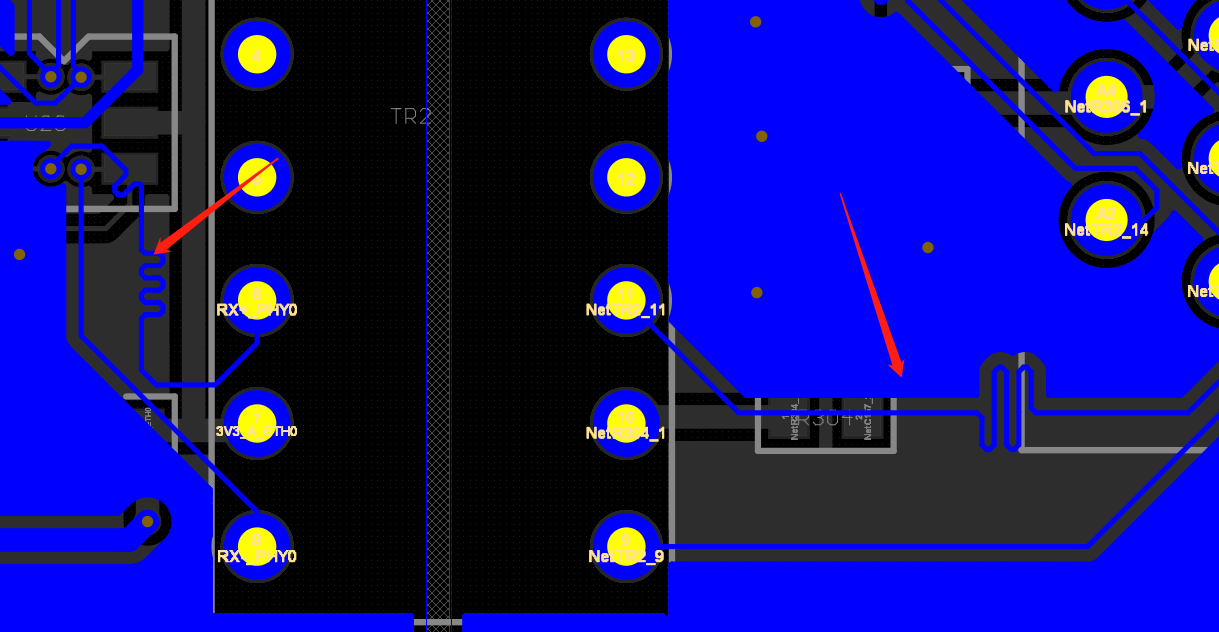

差分走线需要保持耦合从过孔内拉出:此处差分亚需要重新拉出耦合走线,并且差分对内等长需要注意规范:注意高度要小于2S。板上多余线头删除掉:其他的没什么问题了。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以

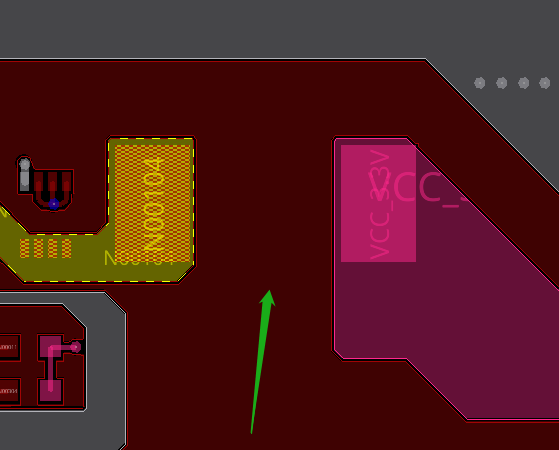

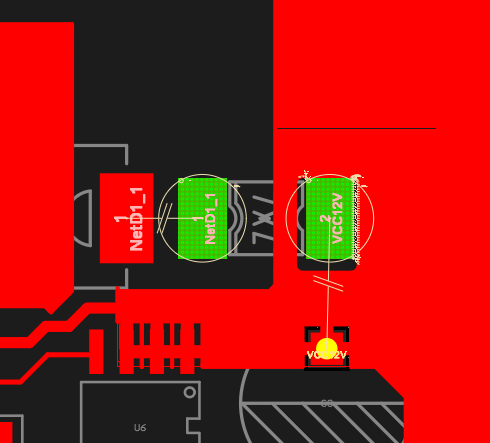

注意电感当前层的内部需要挖空处理:注意反馈信号走8-12MIL就可以了:其他的没什么问题,注意电感内部需要挖空,需要修改的。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:http

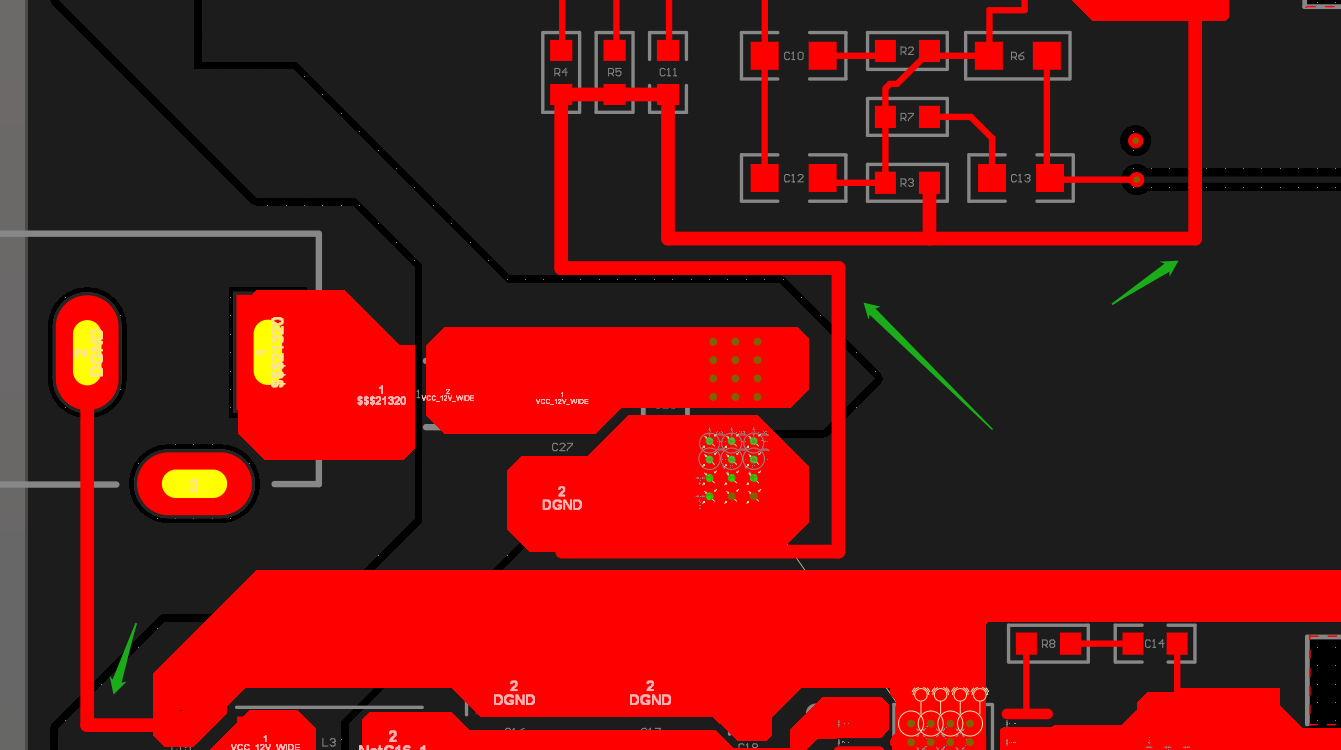

还存在开路报错,自己检查修改下:电感当前层的内部注意放置挖空区域:注意主干道器件需要整体中心对齐,都没 对齐:根据电流输出方向,电容按照先大后小的顺序布局,布局有问题:器件丝印位号没有放置整齐,要不在板外,要不就丝印重叠或者丝印覆盖焊盘了,

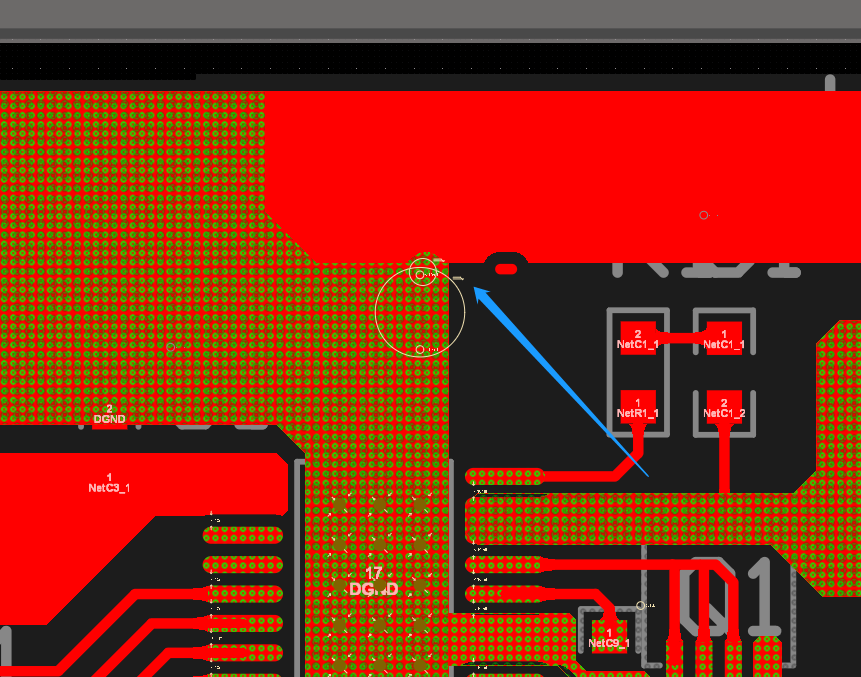

器件在PCB内还存在报错 ,到封装库里面看下此封装是否焊盘上还存在其他东西,删除掉重新导入即可:整板的铜皮注意,不要尖角以及直角,都钝角铺铜:多处需要修整。还存在飞线没有连接:注意布局 是优先电路主干道的器件 其他的配置电阻电容可以远一点放

注意走线规范,不允许直角走线,并且地网络尽量铺铜处理:注意 铜皮绘制不要有尖角:器件注意整体中心对齐:铺铜的铜皮宽度尽量均匀:多余的过孔删掉:焊盘出线不能直接拉出,需要拉出焊盘之后再去拐线处理:整板的走线跟铜皮以及布局都要优化。以上评审报告

电感底部不要放置器件,优化下布局:电感内部的铜皮需要挖掉:信号走线不能从电阻电容内部穿过,优化下走线路径:整体需要特别处理的就是电感底部的电容,不能放在电感底部,需要优化布局。其他的DCDC以及LDO没什么问题。以上评审报告来源于凡亿教育9

扫码关注

扫码关注