- 全部

- 默认排序

在电子电路当中地的种类和作用特别多,大家很容易混淆,其中就有我z们的电源地,信号地,数字地,模拟地等等,不同的地都有不同的作用,在我们进行设计的时候都需要对这些地做特殊的处理才能保证我们板子的信号质量,除了这些地之外那么我们经常说的单点接地

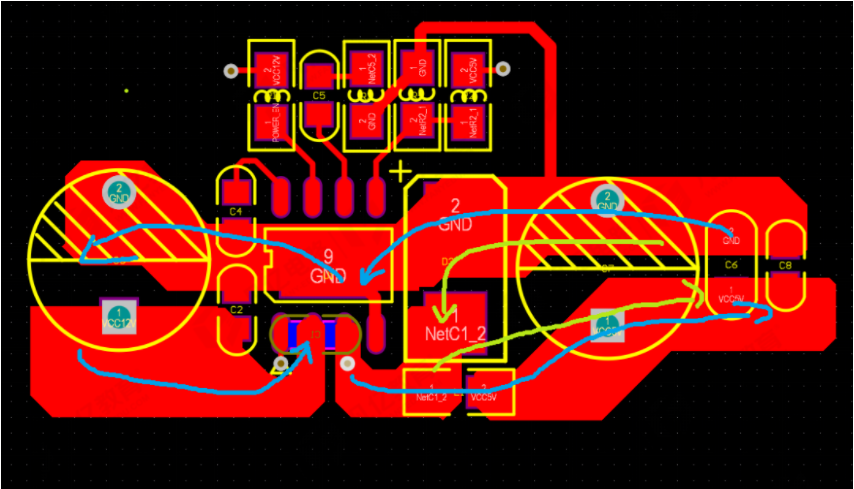

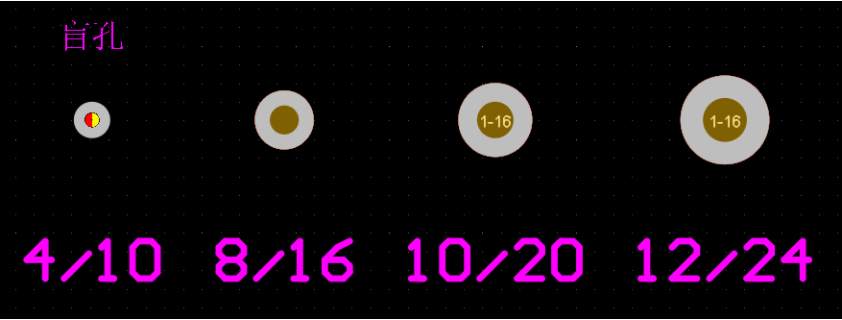

大家在进行PCB设计时过孔肯定是要接触的,那么大家知道过孔对于我们PCB的信号质量影响有多大吗?在搞清楚上面这个这个问题之前我们先给大家介绍一下我们在PCB设计时过孔应该如何选取。一般过孔种类有以下三种可以进行选择:(单位是mil)8/16

1 层叠的定义及添加对高速多层板来说,默认的两层设计无法满足布线信号质量及走线密度要求,这个时候需要对PCB层叠进行添加,以满足设计的要求。2正片层与负片层正片层就是平常用于走线的信号层(直观上看到的地方就是铜线),可以用“线”“铜皮”等进行大块铺铜与填充操作,如图8-32所示。图8-32 正片层

有源晶振与无源晶振的比较

有源晶振不需要DSP的内部振荡器,信号质量好,比较稳定,而且连接方式相对简单(主要是做好电源滤波,通常使用一个电容和电感构成的PI型滤波网络,输出端用一个小阻值的电阻过滤信号即可),不需要复杂的配置电路。

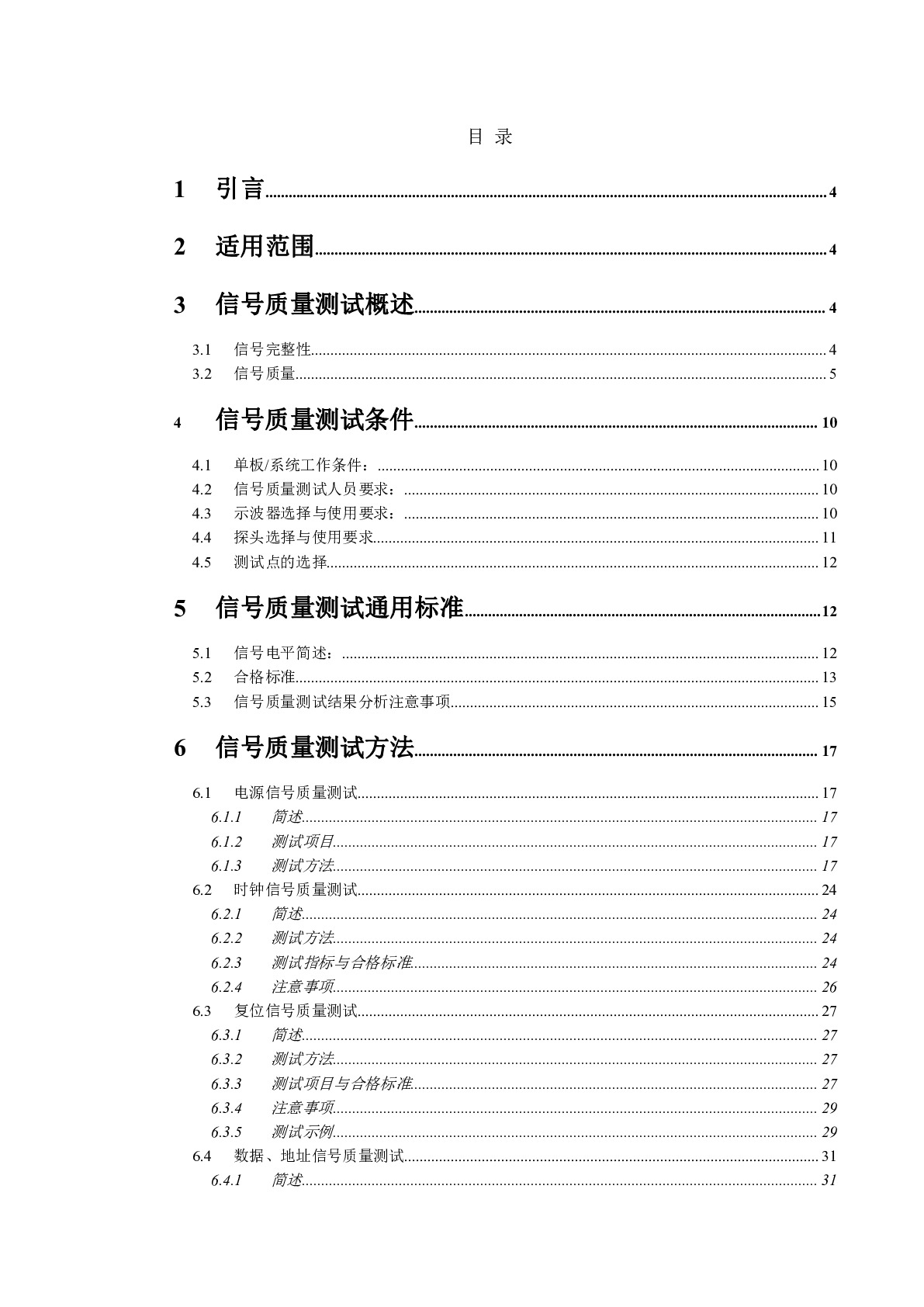

硬件信号质量SI测试规范

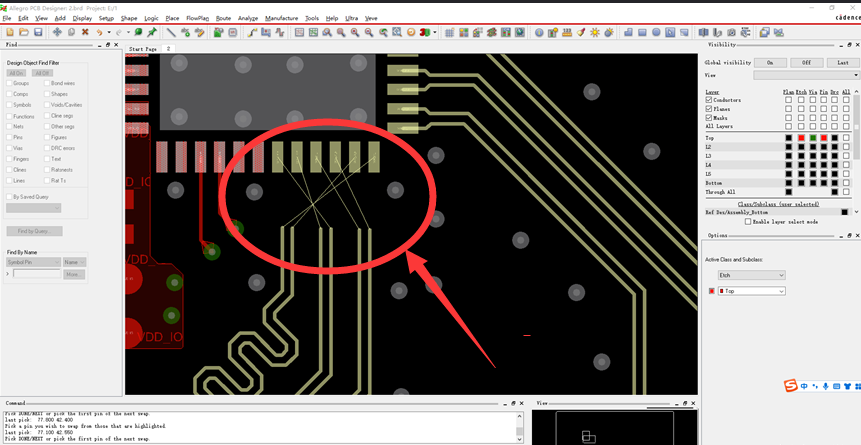

很多电子初学者在使用Cadence Allegro进行Layout设计时,会有一些mipi或lvds等差分走线,在走线时可能为了匹配线序,导致信号网络的走线是交叉,这样做不仅费时费力,还会影响信号质量,那么如何将这些器件的引脚交换过来?如图

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

很多电子小白第一次接触电路板上的元件布局布线,都会头痛,毕竟PCB板上元器件的摆放是一门涉及多学科的技术,需要考虑电路板、布局布线、信号质量、干扰等多种因素,因此,下面来聊聊PCB板上的元器件如何摆放?1、选择合适的放置区域在确定放置区域时

PCB布局,简单来说是工程师综合考虑信号质量、电磁兼容(EMC)、热设计、DFM、结构、DFT等多方面基础上,将多种不同的电子元件合理地放置在PCB板上。布局有多重要?合理的布局是高速PCB设计中的第一步,很多小白都会比较重视布线而忽略布局

全站最新内容推荐

- 1单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

- 2魏信+AD+第四次作业+千兆网口PCB设计作业评审

- 3全能22期- 莱布尼兹的手稿 第十一次作业 SFP

- 4VINKA 高抗干扰18按键触摸芯片/触控感应芯片VK3618I SSOP28/I2C输出功能

- 5工程师秘籍:Perberl转Gerber文件的注意事项

- 690天全能特训班22期AD-空沙-2DDR

- 7电磁兼容中EMI骚扰源特征

- 8USB3.0 HUB方案之VL813

- 990天全能特训班22期Allegro-莱布尼兹的手稿-SATA

- 10pads2.14软件120讲速成+2层实战项目视频教程

扫码关注

扫码关注