- 全部

- 默认排序

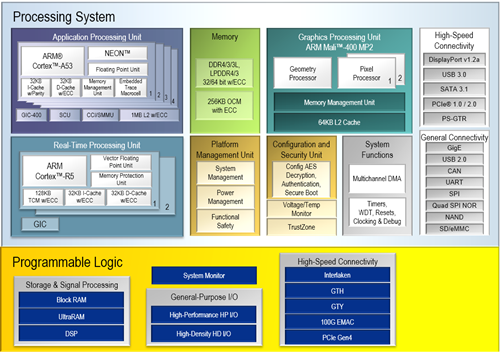

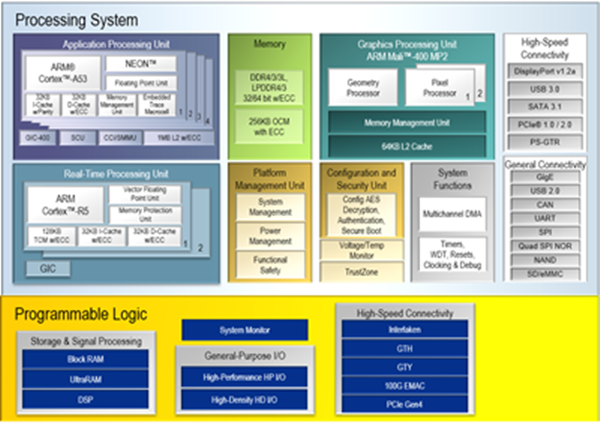

产品简介Zynq® Ultrascale+™ MPSoC 器件不仅提供 64 位处理器可扩展性,同时还将实时控制与软硬件引擎相结合,支持图形、视频、波形与数据包处理。 三个不同变体包括双应用处理器 (CG) 器件、四核应用处理器和 GPU

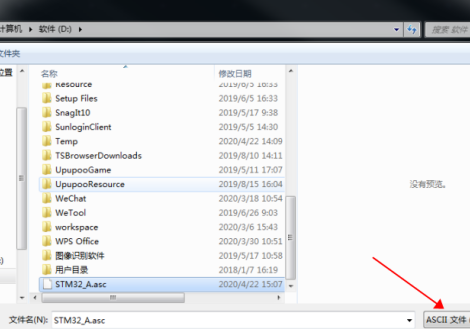

1.allegro16.6已经打了102号补丁,已经将AD工程里的原理图转化为ascII格式,并且编译过有PrjPCBStructure后缀文件,使用file-importAltiumschematicc,报脚本出错,如图所示。2.设置好路径之后,点击转换报错无法找到路径,如图所示。3.在文件夹下能

产品简介Zynq™ Ultrascale+™ MPSoC 器件基于业内最先进的16nm FinFET+工艺制程打造,整合了64位ARM Cortex-A53处理器、512位ARM Mali-400 MP2图形处理器以及可编程逻辑单元,具有强

Zynq® Ultrascale+™ MPSoC 器件不仅提供 64 位处理器可扩展性,同时还将实时控制与软硬件引擎相结合,支持图形、视频、波形与数据包处理。 三个不同变体包括双应用处理器 (CG) 器件、四核应用处理器和 GPU (EG)

若是评选世上最受欢迎的EDA软件,Mentor Pads必有一席之地,这也吸引了很多电子工程师去学习Pads软件,在学习过程中可能会遇见这些问题,如使用Pads软件导出原理图文件(如dxp、ascII等格式),发现导出的汉字文件却变成了乱码

根据最近的 ascE 数据,在美国,每两分钟就有一条水管破裂,每天泄漏的水足以填满 9,000 个游泳池。随着关键基础设施的不断老化,公用事业和市政当局必须找到切实可行的解决方案,用现代材料和技术重建和增强这些系统。事实上,根据美国自来水厂

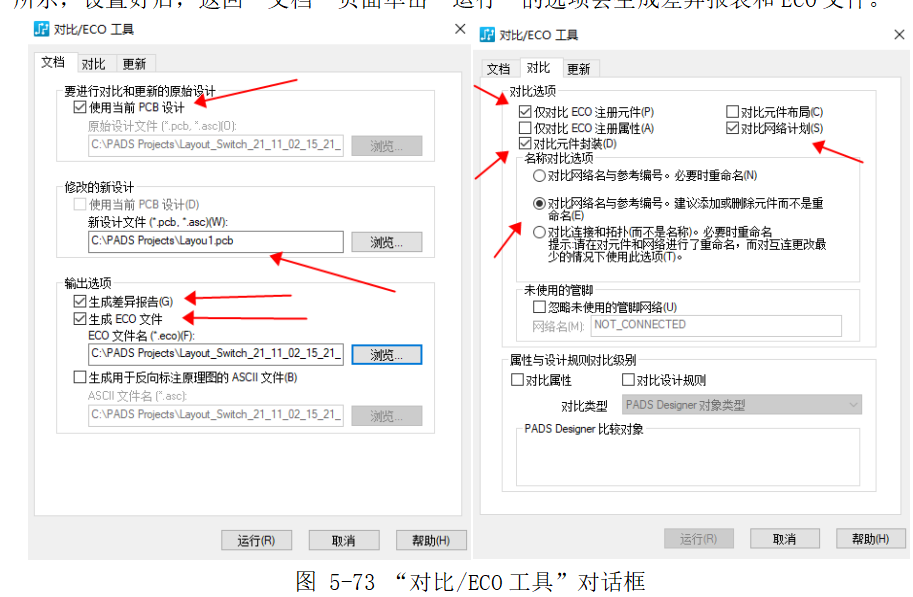

若原理图非Logic格式,是其他软件生成的.asc文件导入,设计中有更改,需要更新PCB,则可利用ECO网络对比功能,进行PCB的更新。1)执行菜单命令“工具-对比/ECO”,如图5-73所示。将当前正在设计的PCB文件和更新中的PCB对比

PADS Layout导入网表,即将原理图与PCB进行同步,具体步骤可参考“4.6.1 PADS Logic与layout同步操作”内容。除了导入Logic原理图文件,还可将Orcad原理图导出的asc文件导入到Layout内。1)执行菜单

扫码关注

扫码关注