- 全部

- 默认排序

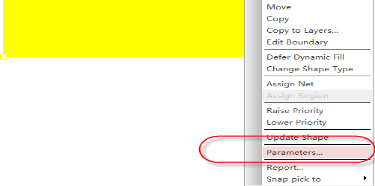

答:做PCB设计时,有些区域可以设置禁止铺铜,但是允许走线。第一步,点击Setup-Areas-Shape Keepout,在需要禁止铺铜的区域画好禁示区域,如图6-327所示;

答:orcad创建封装库时,放置管脚的Shape的含义是管脚的长度以及一些特殊含义,其表示的含义解释如下:Clock:时钟信号,管脚的长度是标准长度;Dot:低电平有效信号,管脚的长度是标准长度;Dot-Clock:低电平有效的时钟信号,管脚的长度是标准长度;Line:普通信号,管脚的长度是标准长度;Short:普通信号,管脚的长度比标准的长度要短一些;Short Clock:时钟信号,管脚的长度比标准的长度要短一些;Short Dot:低电平有效信号,管脚的长度比标准的长度要短一些;Short

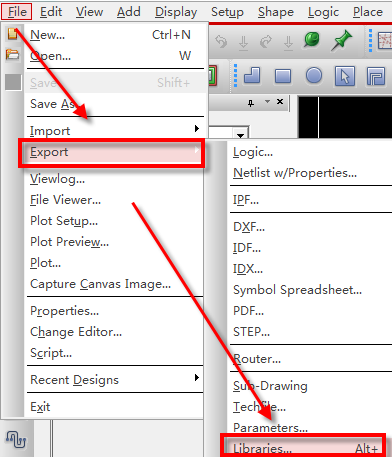

答:在导网表时,如果碰到有缺失Flash的报错,而正好缺失的Falsh在另一个项目中使用过,我们可以从另一个PCB中调用,具体的步骤如下:第一步,打开PCB,点击File-Export-Libraries…,在弹出的对话框中勾选Shape and flash symbols、No library dependencies选项,设置好导出的文件夹路径,点击Export导出,如图4-111所示;

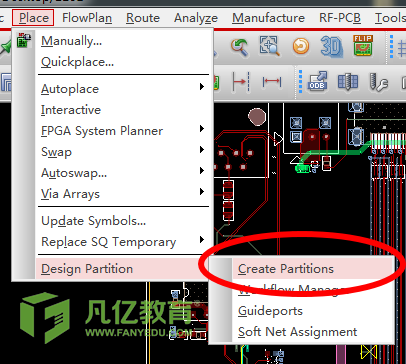

一、首先打开需要多人协助的板子,allegro点击选择Place ---Design---Create Partitions选项。二、点击进去以后,Options 栏下面 显示如下界面。三、右键点击板子空白处右键,选择加一个Shape 或者选择加一个矩形框。四、选择完成以后,开始框选你想要分出去的那一块。如下图,白色线框内既为要分出去的板块。

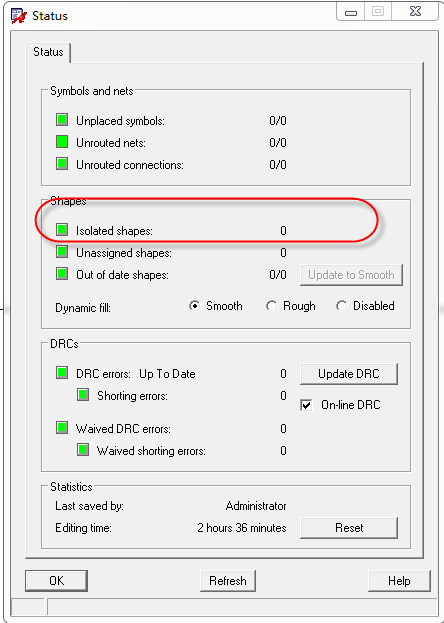

孤铜也叫孤岛(Isolated Shapes),也叫死铜,如图12-16所示,是指在PCB中孤立无连接的铜箔,一般都是在铺铜时产生的,不利于生产。解决的方法比较简单,可以手工连线将其与同网络的铜箔相连,也可以通过打过孔的方式将其与同网络的铜箔相连。无法解决的孤铜,删除掉即可。

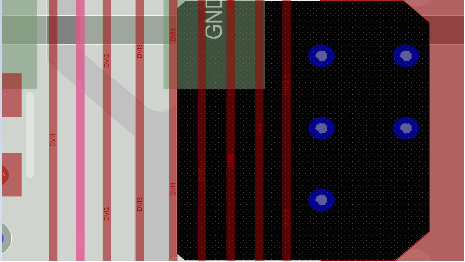

答:一般在使用Allegro软件设计时,铺铜都会铺实铜,但是对于如FPC设计,通常需要铺网格铜,以满足PCB的弯折性要求。具体操作的步骤如下所示:第一步,首先使用Shape-Polygen选项,在PCB上画一个铜皮,此时画出来的铜皮是实心的,如图6-297所示;

答:孤岛铜皮, Isolated Shapes,也叫做孤岛,指的是在PCB中孤立、没有与任何地方连接的铜箔。在Allegro软件中,系统会自动统计孤岛铜皮的个数,如图1-49所示,对于PCB板上的孤岛铜皮,一般我们在设计的时候,对于很大块的孤岛铜皮,我们尽量在这个铜皮打上地过孔。让铜皮接地,使整个PCB地连接性更好;而对于面积很小的孤岛铜皮,我们选择删除,点击shape-Delete Island,就可以把整个孤岛铜皮给删除掉,如如1-50所示。孤岛铜皮的存在,主要是会与周

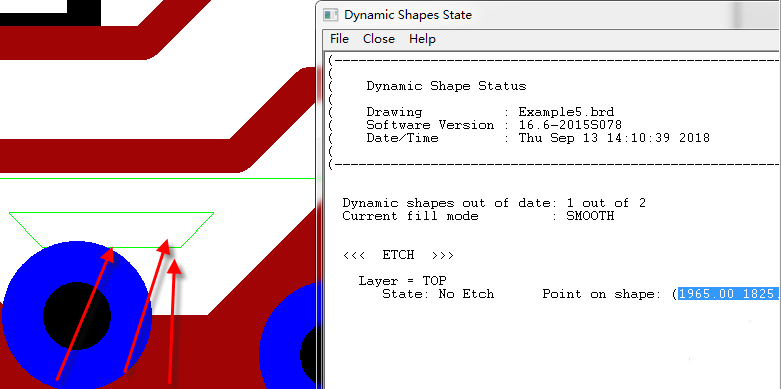

答:我们在设计完成之后,需要对所有的铜皮进行smooth处理,在进行smooth处理的时候,有时因为铺铜的错误操作,出现有一块或者几块铜皮不能更新,出现Out of data shape的问题,如图6-188所示,

1、覆铜覆盖焊盘时,要完全覆盖,shape 和焊盘不能形成锐角的夹角。2、尽量用覆铜替代粗线。当使用粗线时,过孔通常为非通常走线过孔,增大过孔的孔径和焊盘。修改后:3、尽量用覆铜替换覆铜+走线的模式,后者常常产生一些小尖角和直角使用覆铜替换

扫码关注

扫码关注