- 全部

- 默认排序

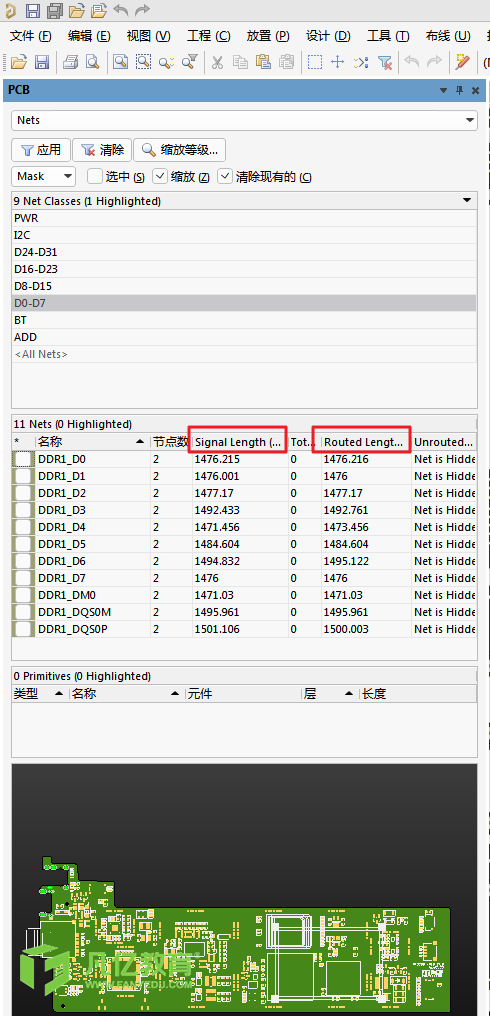

在使用Altium Designer画PCB时,等长布线后,使用快捷键R+L检测布线长度时,发现布的线长不一致,在PCB的nets里查看长度时看到了Signal length和Routed length

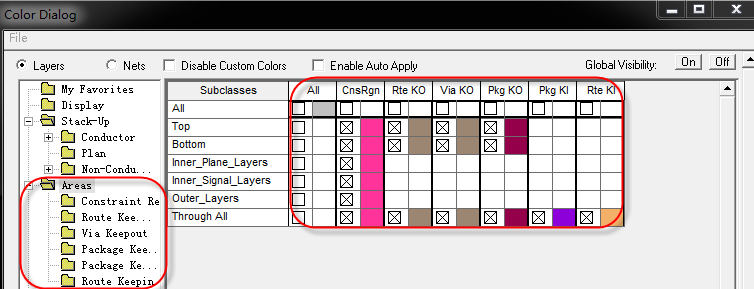

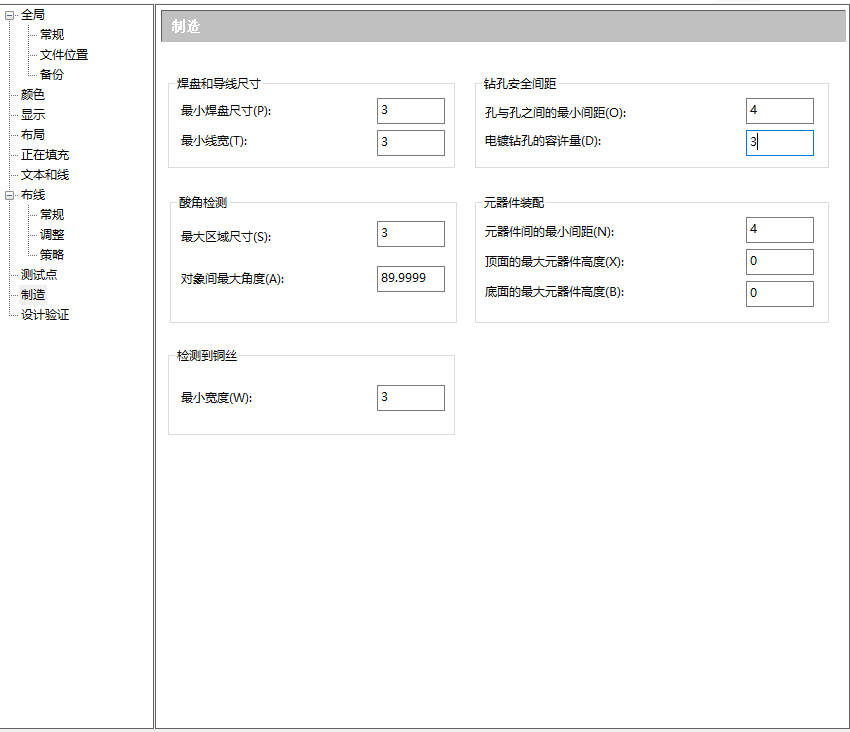

我们在进行PCB设计的时候,需要根据不同的PCB板结构以及一些电子产品的需求来进行各种不同区域的设计,包括允许布局区域设计、禁止布局区域设计。允许布线区域设计等等。在Allegro设计中,设置这些就在Areas,如图5-60所示。 图5-60 各类布局布线区域示意图Ø 在Allegro软件中有Route Keepout、Route Keepin、Package Keepout、Package Keepin、Via Keepout等多种类型的区域进行设置,对PCB工

Explosion-proof is required in hazardous areas such as combustible or flammable gases, vapours, dust, fibres and flyings

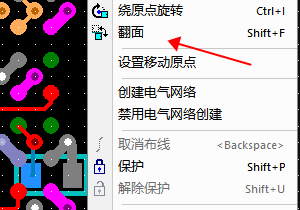

Router组件布局移到器件操作与Layout组件基本类似。移动快捷键为“Ctrl+E”,翻转换面快捷键为“Shfit+F”。1)在操作界面右击选择“选择器件”项,然后在PCB内点击器件,按快捷键“Ctrl+E”,然后移动鼠标可将器件移动。

老师,AD20 ActiveRoute功能使用有没有详细的操作步骤!网上看到一些步骤,在AD19上操作失败,多条线一起走,只有那一条很粗的线,没有分开,是什么原因?请指教!!!

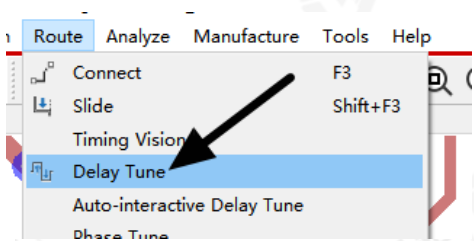

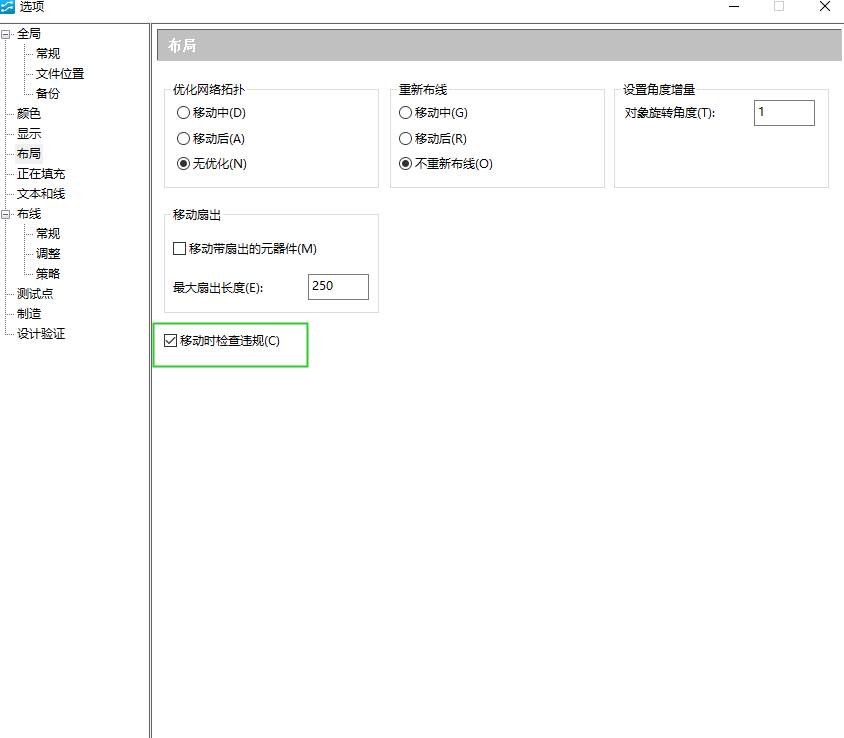

在PCB设计中做等长时,常常会用到蛇形走线,下面就介绍一下如何进行蛇形走线及相关设置:执行菜单面临Route-Delay Tune,在Options进行相关设置,其中Style是蛇形等长的样式,Gap一般设置为3倍线宽,Corners角度一

扫码关注

扫码关注