- 全部

- 默认排序

蛇形走线和码间干扰是高速PCB设计中需要关注的两个重要问题,在布线阶段若是没处理好蛇形走线和码间干扰,容易影响到系统性能和稳定性,下面讲讲如何处理这两个问题,希望对小伙伴们有所帮助。蛇形走线是一种常用的布线方式,可以降低信号线之间的互相干扰

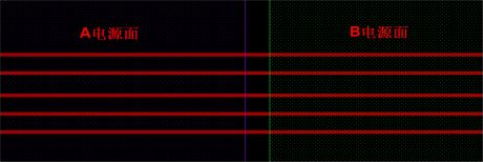

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割现象示意图跨分割,对于低速信号可能没有什么关系,但是在高速

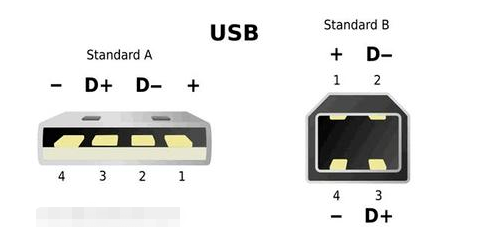

超详细的USB PCB设计规范USB是一种快速、双向、同步传输、价格便宜、方便使用的可热拔插的串行接口。由于数据传输快,接口方便,支持热插拔等优点使USB设备得到广泛应用。目前,市场上以USB2.0为接口的产品居多,但很多硬件新手在USB应

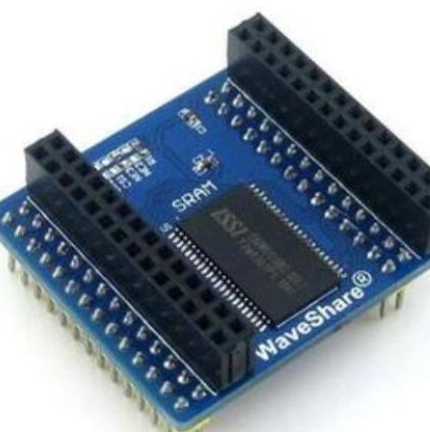

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:

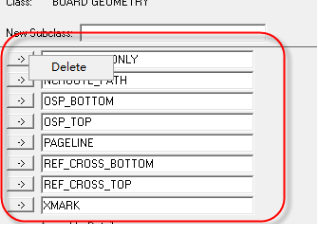

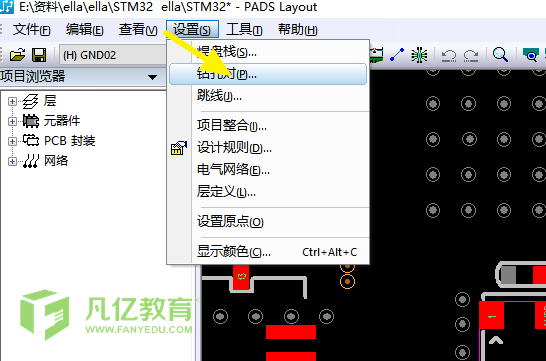

答:我们在进行PCB设计的时候,导入DXF文件后者其它参照的对象,都会在PCB中新建一些subclas层,累计的多了,subclass层就会非常多,所以我们这里讲解一下,如何去删除自己新建的subclass层,具体操作如下所示:

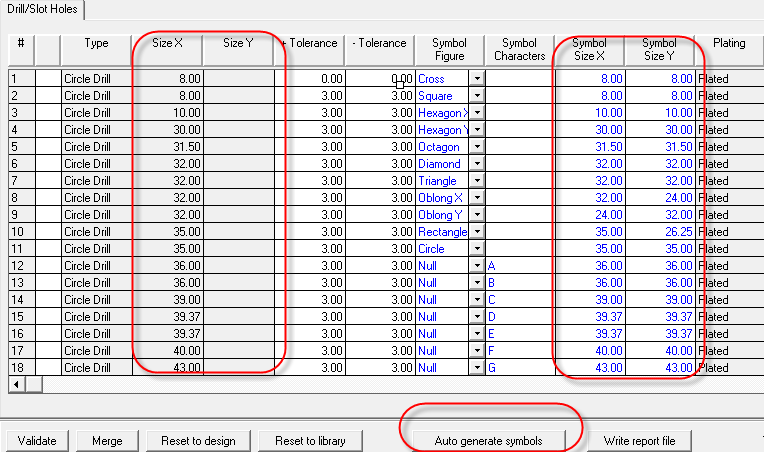

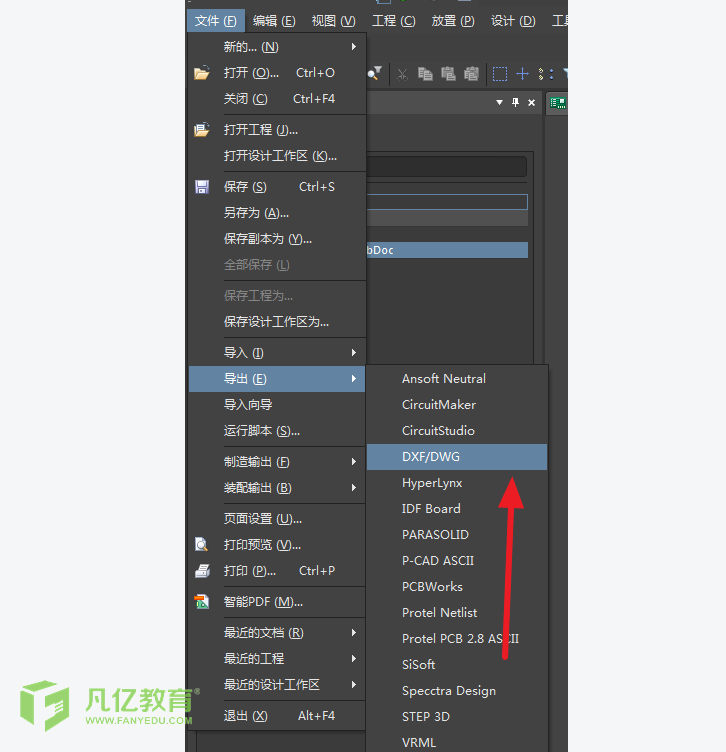

答:我们直接从Allegro软件导出的DXF文件,通孔的器件一般都只有焊盘,是没有钻孔数据的,也就是没有内径,如图6-167所示,我们这里给大家介绍一下,如何导出含有钻孔数据的DXF文件,具体操作如下所示:

我们在之前的学习中,学过DXF结构文件的导入,因为我们有时候设计PCB的时候,会碰到异形的板框,那么我们就要用DXF文件将结构图导入进PCB中,然后再进行板框制作,最后再进行PCB设计

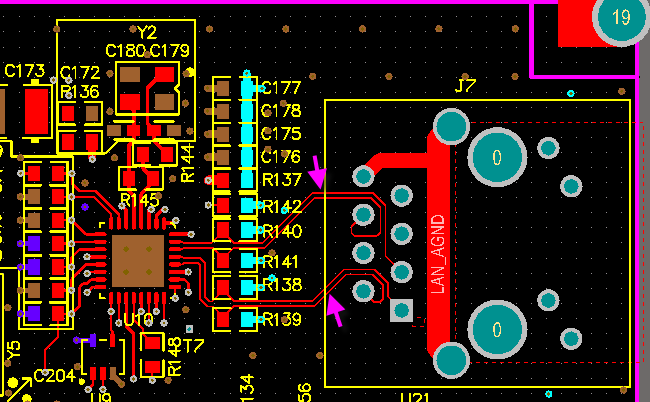

以太网(Ethernet)是一种计算机局域网组网技术,该技术基于IEEE制定的IEEE 802.3标准,它规定了包括物理层的连线、电信号和介质访问层协议的内容。 以太网是当前应用最普遍的局域网技术。Ethernet的接口是实质是MAC通过MII总线控制PHY的过程。

全站最新内容推荐

- 1LED驱动模块RSC6218A 5W-18W迷你高效驱动电源应用-REASUNOS(瑞森半导体)

- 2从零开始成为电子大佬,第一步先识读电源!

- 3IEEE 1588 四通道/八通道系统同步器:8A34001E-000AJG、8A34002E-000NLG、8A34003E-000NBG(器件)

- 4光电器件故障了,如何排除维护?

- 5走进电子元器件,了解热继电器

- 6搞电子设计的人,转行能干什么?

- 7Solder Mask和Paste Mask有哪些不同?

- 8PCB板制造技术水平的标志如何看?

- 9雷军招人:为中国汽车工业全面崛起做贡献!

- 10单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

扫码关注

扫码关注