- 全部

- 默认排序

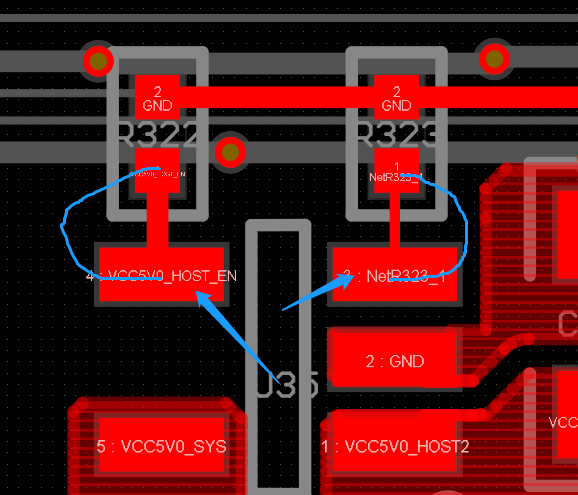

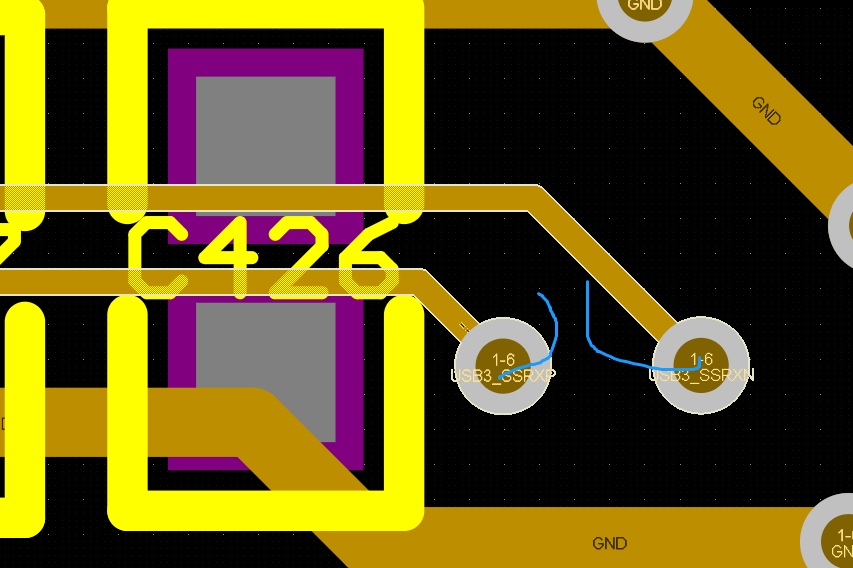

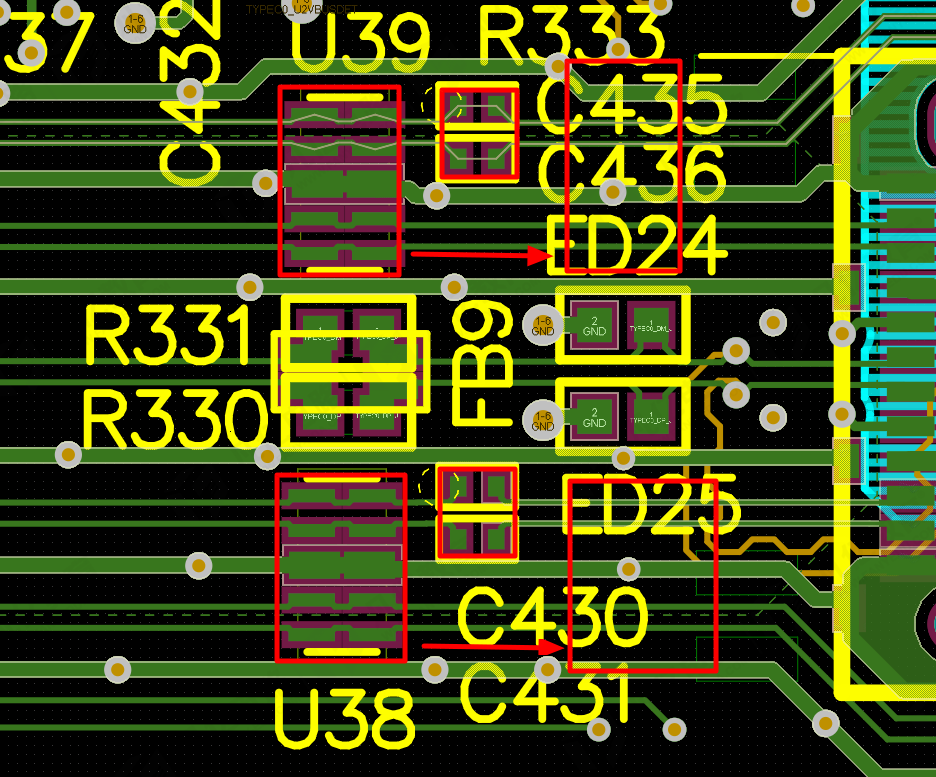

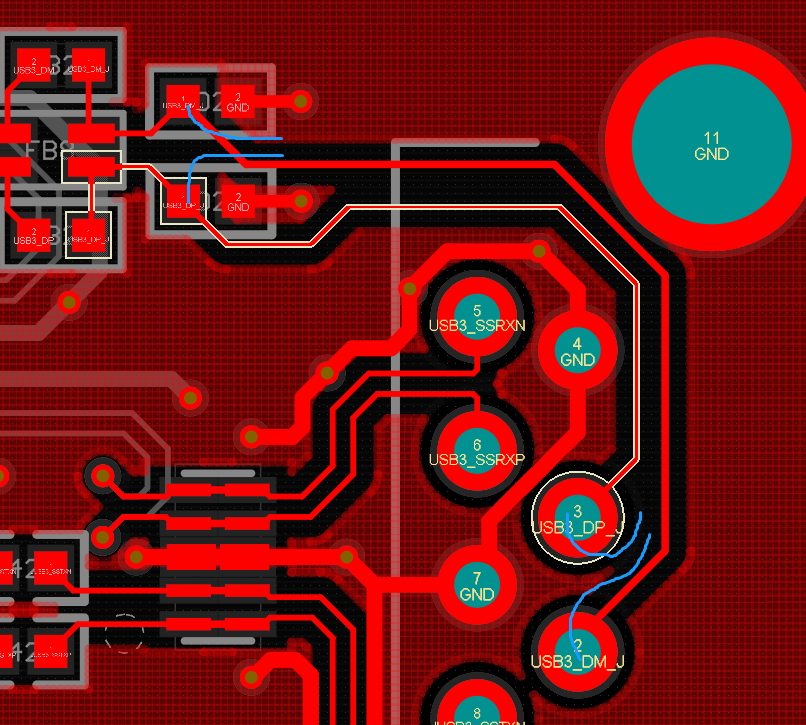

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.差分线处理不当,锯齿状等长不能超过线距的两倍3.差分对内等长误差5mil4.此处需要经过ESD器件在到USB座子5.地网络直接就近打孔即可以上评审报告来源于凡亿教育90天高

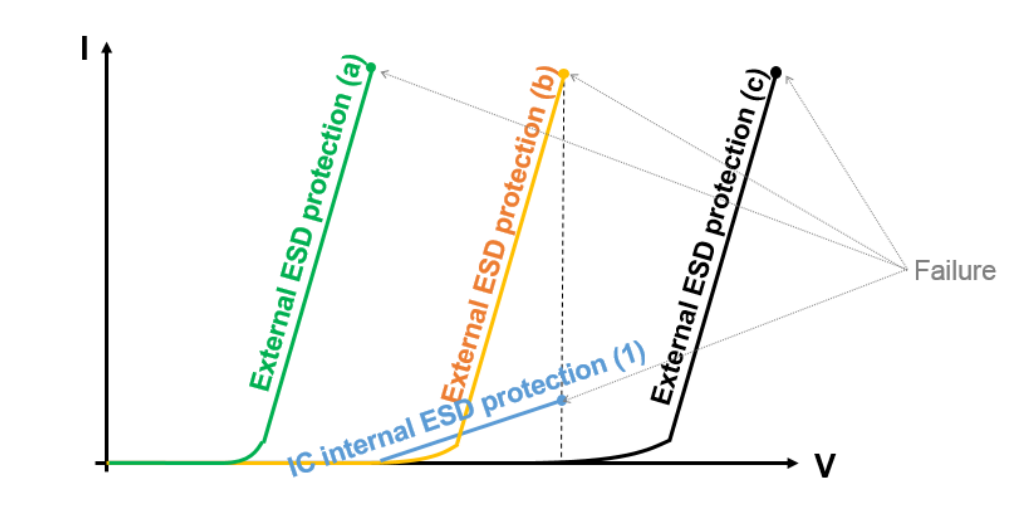

平时通过走路穿衣等日常活动带来的摩擦,会产生不同幅值的静电电压,但其能量很小不会对人体产生伤害,不过对于电子元器件来说,这种静电能量却是不能忽视的。在干燥的环境下,人体静电(ESD)的电压很容易超过6~35Kv,当用手触摸电子设备、PCB或

静电放电(ESD)是在电子产品和PCB设计中常见的问题之一,若是处理不当,极有可能对电子元件和线路板造成永久性伤害,降低产品的可靠性,因此很多工程师遇见PCB板有ESD现象就要着手处理。1、为什么会产生静电放电现象?首先,了解ESD的来源是

差分走线注意出线耦合2.注意焊盘出线规范3.差分对内等长不规范,锯齿状等长,凸起高度不能超过线距的两倍4.注意打孔要打在ESD器件前面,先经过ESD器件5.器件摆放不要挡住1脚标识6.USB差分需要进行对内等长,误差5milUSB2.0电源

1.ESD器件应该尽量考近USB接口,放置的顺序是ESD-共模电感-阻容。2.差分对内等长误差控制在5mm以内。3.差分走线尽量保持在一层走线,避免一层走一半,换层在两端完成。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解

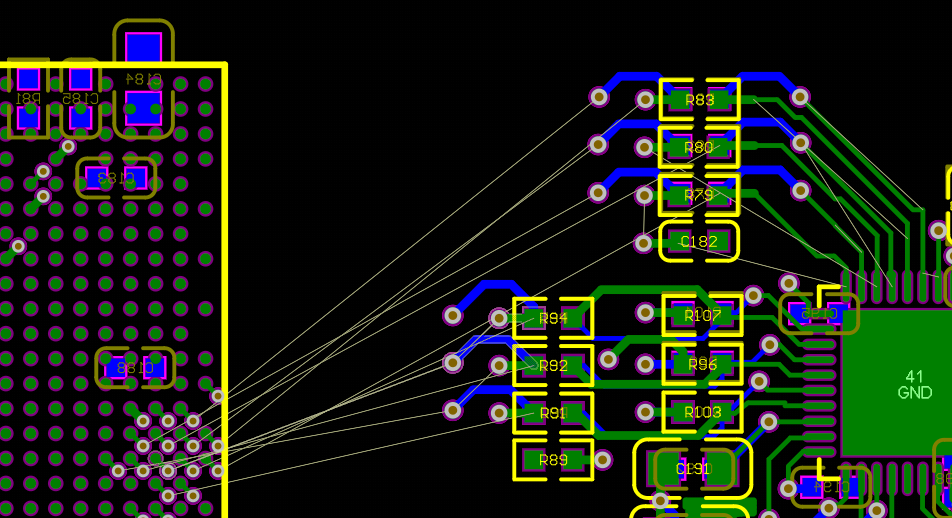

作业未完成。很多布线、过孔没有网络,线宽不一致导致阻抗不连续、有直角。铜皮避让中间没连上,应该在铜皮属性栏换个链接方式。存在多处开路器件摆放干涉差分出线不耦合前后不一致,差分ESD器件就近打孔差分走线不耦合,没有对内等长。变压器下面没有铺铜

注意差分出线要尽量耦合,走一起2.注意差分走线需要按照阻抗线宽线距走线,否则容易产生阻抗突变3.打孔要打在ESD器件前面4.走线一层连通不用打孔差分需要进行对内等长,误差5mil差分对内等长凸起高度不能超过线距的两倍注意器件摆放不要干涉一脚

随着电子技术和集成电路的发展,电子工业设备越来越多功能化、智能化,然而搞集成电路元件容易受到静电放电的影响,带来一系列的麻烦,因此研究电子工业中的静电源和防护措施是很有必要的。一般来说,静电放电(ESD)的原理是指两个物体处于不同的电位,却

扫码关注

扫码关注