- 全部

- 默认排序

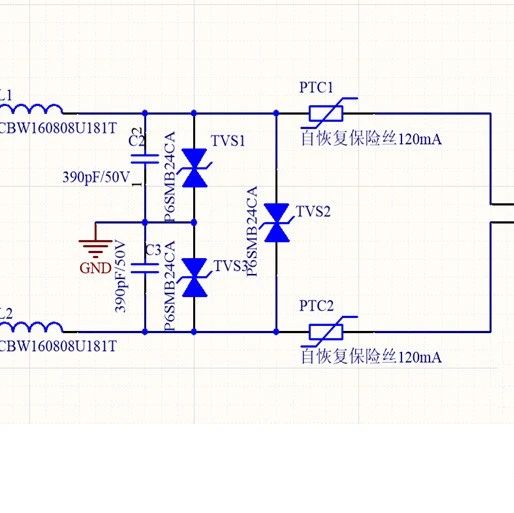

RS485电路原理图设计

RS485是差分信号,半双工、平衡传输线多点通信的标准,两个设备之间使用双绞屏蔽线缆连接,两个线缆分别传输A和B信号。RS485的传输速率与总线长度相关,最高可以达到10Mb/s,线缆越长,速率越慢;线缆越短,速率越快;RS485总线具有两种逻辑电平:高电平(1)和低电平(0)高电平(1):B线上的

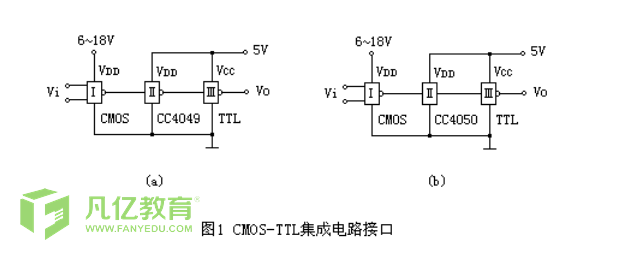

了解CMOS集成电路的技术参数及特性,有助于更好地帮助我们提高集成电路的设计效率,也能进一步巩固我们的自身基础知识,所以今天我们将详谈CMOS集成电路的技术参数及特性。1.标称逻辑电平门电路的逻辑功能是通过指定高电平表示1,低电平表示0来实

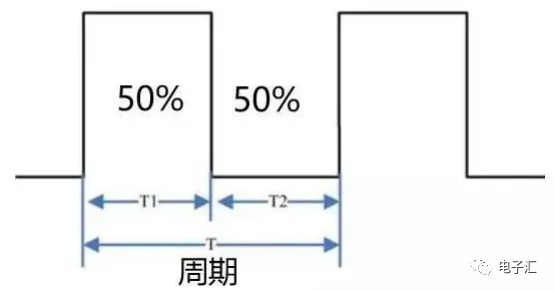

什么是PWM脉冲宽度调制(PWM),是英文“Pulse Width Modulation”的缩写,简称脉宽调制,是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术,广泛应用在从测量、通信到功率控制与变换的许多领域中。pwm的频率:是指1秒钟内信号从高电平到低电平再回到高电平的次数(一个

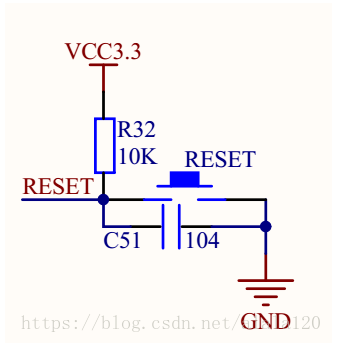

0组成:电源 复位 时钟 调试接口 启动1、电源 : 一般3.3V LDO供电 加多个0.01uf去耦电容2、复位:有三种复位方式:上电复位、手动复位、程序自动复位通常低电平复位:(51单片机高电平复位,电容电阻位置调换)上电复位,在上电瞬

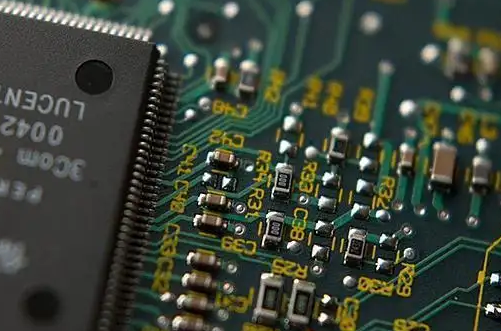

高速PCB设计指南之六

高速PCB设计指南之六第一篇 混合信号电路板的设计准则 模拟电路的工作依赖连续变化的电流和电压。数字电路的工作依赖在接收端根据预先定义的电压电平或门限对高电平或低电平的检测,它相当于判断逻辑状态的“真”或“假”。在数字电路的高电平和低电平之间,存在“灰色”区域,在此区域数字电路有时表现出模拟

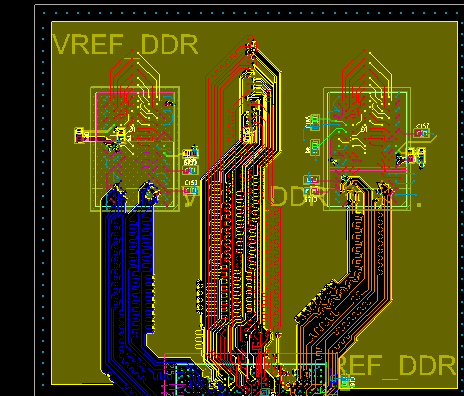

这个vref是参考电压,写入或读取数据时需要用vref来确定是高电平还是低电平,不要大面积铺铜。四块的也是一样ddr到芯片的距离有点远了一般是600-800mil丝印位置可以调一下,调整齐不放焊盘上其他的没什么问题以上评审报告来源于凡亿教育

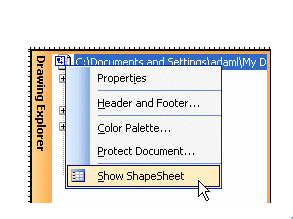

答:orcad创建封装库时,放置管脚的Shape的含义是管脚的长度以及一些特殊含义,其表示的含义解释如下:Clock:时钟信号,管脚的长度是标准长度;Dot:低电平有效信号,管脚的长度是标准长度;Dot-Clock:低电平有效的时钟信号,管脚的长度是标准长度;Line:普通信号,管脚的长度是标准长度;Short:普通信号,管脚的长度比标准的长度要短一些;Short Clock:时钟信号,管脚的长度比标准的长度要短一些;Short Dot:低电平有效信号,管脚的长度比标准的长度要短一些;Short

扫码关注

扫码关注