.9 PCB设计后期处理

处理完连通性和电源之后,需要对整板的情况进行走线优化调整,以充分满足各类EMC等要求。

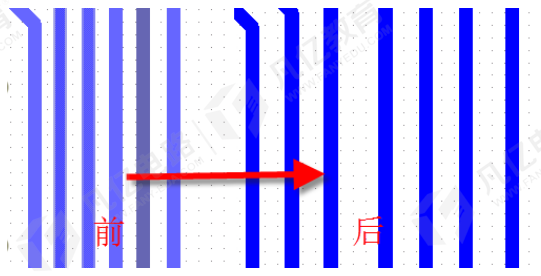

.9.1 3W原则

为了减少线间串扰,应保证线间距足够大,当线中心距不少于3倍线宽时,则可保证70%的线间电场不互相干扰,这称为3W原则。如图11-23所示,修线后期需要对此进行优化修整。

图11-23 3W原则优化

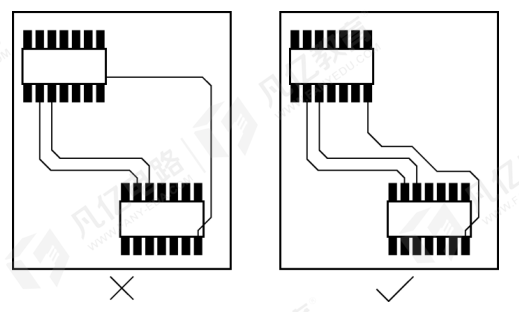

.9.2 修减环路面积

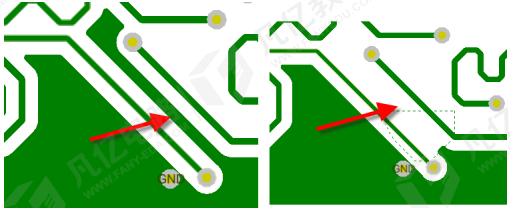

电流的大小与磁通量成正比,较小的环路中通过的磁通量也较小,因此感应出的电流也较小,这就说明环路面积必须最小。如图11-24所示,尽量在出现环路的地方让其面积做到最小。

图11-24 修减环路面积

.9.3 孤铜及尖岬铜皮的修整

为了满足生产的要求,PCB设计中不应出现孤铜。如图11-25所示,可以通过设置覆铜方式避免出现孤铜。如果出现了,应按照前而提到过的去孤铜的方法进行移除。

图11-25 移除孤铜

为了满足信号要求(不出现天线效应)及生产要求等,PCB设计中应尽量避免出现狭长的尖岬铜皮。以图11-26为例,可以通过放置禁布区删除尖岬铜皮。

图11-26 修铜

.9.4 回流地过孔的放置

信号最终回流的目的地是地平面,为了缩短回流路径,在一些空白的地方或打孔换层的走线附近放置地过孔,特别是在高速线旁边,可以有效地对一些干扰进行吸收,也有利于缩短信号的回流路径。

.10 本章小结

本章是一个入门级别的实例,不过不再是2层板,而是一个4层板。这是一个高速PCB设计的入门实例,同样是以实际流程进行讲解,可以进一步加深读者对设计流程的把握,同时开始接触高速PCB设计的知识,为PCB技术的提高打下良好的基础,为迎接实际工作做好准备。

扫码关注

扫码关注