9.7 PADS Router设计布线操作

1.布线与修线操作

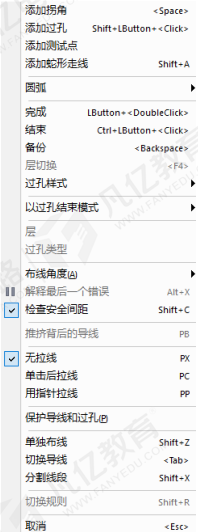

(1)布线前需将规则设置好,一般在PADS Layout内添加规则及层叠,注意将布线层选中。在Router组件执行菜单命令【工具】→【选项】,在“选项”对话框“布线”标签页进行参数设置。注意选择好“布线角度”、“交互式布线”等参数,层对设置顶底层,一般不建议打开“拉线器”,如图9-32所示。

图9-32 布线参数设置

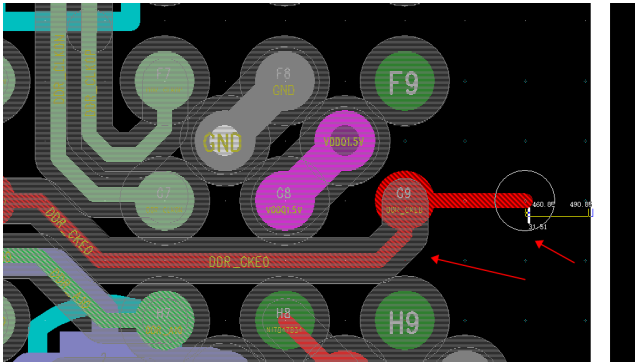

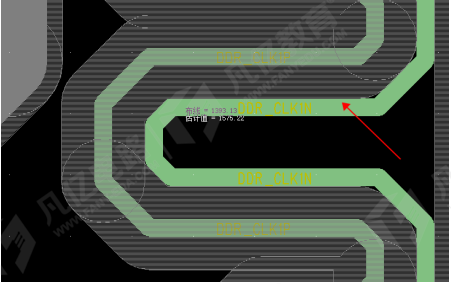

(2)设置布线格点,设计格点及显示格点使用无模命令设置为5mil,到PCB中按“F3”键,再单击焊盘,可以进行拉线处理。正在布线的信号会高亮显示,布线及焊盘白色边缘为“保护带”,如图9-33所示。

图9-33 拉线

(3)若对布线情况不满意,可使用组合快捷键“SHIFT+S”进行修线处理。在英文输入状态下使用快捷键“SHIFT+S”,出现“V”字标识,然后选中需要进行调整的线进行微调。

(4)若需要对部分信号线进行删除,按“Backspace”键,选中线即可删除,若需要删除多条线,可以利用“Shift+鼠标左键”进行多选,然后删除。

2.过孔操作

(1)先在PADS Layout内设置好过孔类型,然后在“过孔配置”选项页将使用的过孔勾选。

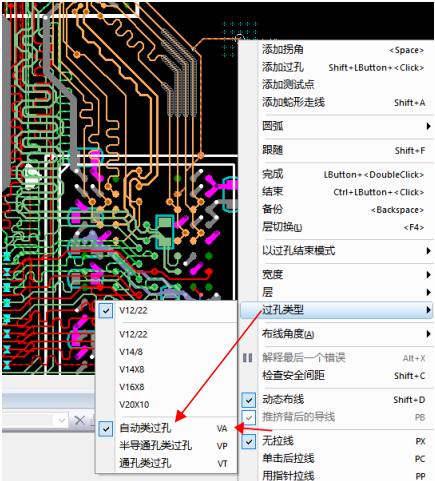

(2)有多个过孔类型,可以先指定当前设计时使用的过孔类型。布线操作期间,右击在“过孔类型”内选择“通孔类过孔”或者“自动类过孔”命令,选择当前设计需要用到的过孔类型,如图9-34所示。

图9-34 过孔类型选择

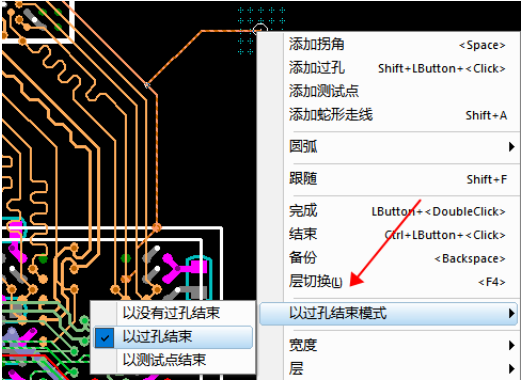

(3)拉线期间右击,在“以过孔结束模式”内选择过孔结束模式,若选择“以过孔结束”,命令则在布线期间使用“Ctrl+鼠标单击”可将过孔添加到PCB内。建议选择“以没有过孔结束”命令,配合在拉线期间使用“F4”快捷键,可在布线时添加过孔,代替“Ctrl+鼠标单击”功能,而让“Ctrl+鼠标单击”执行布线结束命令。过孔扇出时需注意DRC,若生成过孔的位置有焊盘或者其他信号布线,则会导致添加过孔失败,可打开所有层在空白处理添加过孔,或者添加过孔时关闭DRC开关,过孔添加后进行修线处理,如图9-35所示。

图9-35 “过孔结束模式”选择界面

(4)除了上述添加过孔方式,还可在PCB右击选择“选择网络”命令,通过单击焊盘或者信号线选择网络,右击选择“添加过孔”命令,会生成此网络的过孔,将过孔放置到PCB内合适位置,注意若有DRC,过孔会添加失败,如图9-36所示。

图9-36 “过孔结束模式”界面选择

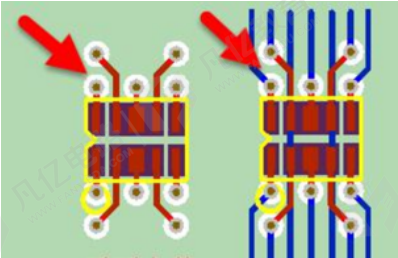

(5)常规过孔扇出方式建议如图9-37所示。

图9-37 常规过孔扇出方式

3.BGA扇出介绍

(1)BGA扇出前需设置好规则,将BGA下方器件挪走,所有层布线清除,若扇出时有DRC产生,会导致扇出失败。扇出前将格点设置为PIN间距的一半或者0,设置为PIN间距一半时需将精度设置好,否则会导到设置的格点4舍5入,设置失败。选择好合适的过孔,一般BGA扇出会选择8mil的过孔,过孔孔径太大会导致DRC产生。

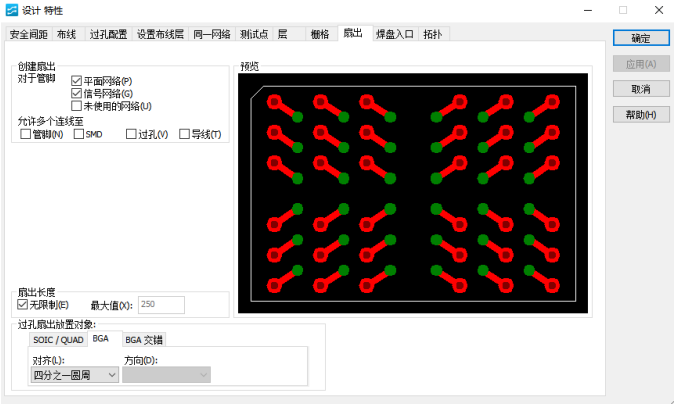

(2)在PCB空白处双击,在弹出的“设计特性”界面的“扇出”页将选项设置好,如图9-38所示。

图9-38 扇出页设置

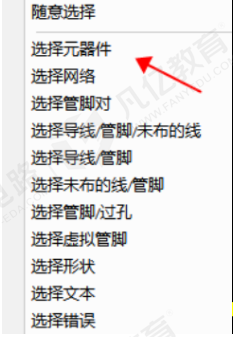

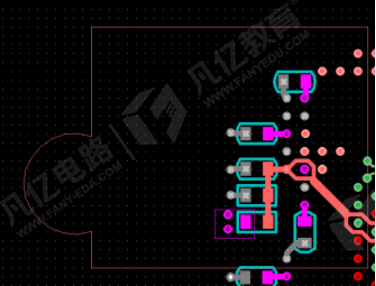

(3)在PCB空白处右击选择“选择元器件”命令,在PCB中选择器件,右击选择“扇出”命令,软件会自动对BGA器件进行过孔扇出,如图9-39所示。

图9-39 扇出过孔

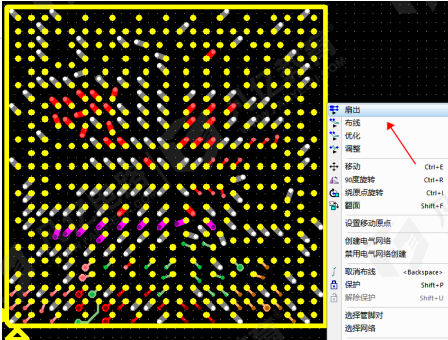

(4)推荐的扇出方式如图9-40所示,BGA中间留有十字通道以满足IC电源载流。

图9-40 推荐BGA扇出方式

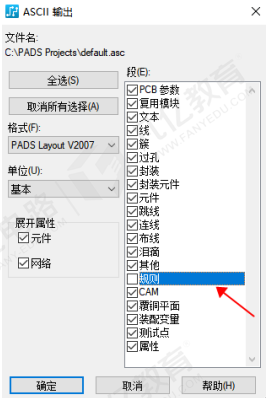

(5)若扇出失败是因规则设置错误而有DRC产生导致,可到PADS Layout组件内设置好规则,若规则设置太多,搞不清楚是哪个规则导致,则可将PCB内部所有规则删除,再重新设置。在PADS Layout内执行菜单命令【文件】→【导出】,导出ASC文件,导出时不选择“规则”选项,则会消除PCB内部全部规则,然后将此ASC文件导入新的PCB内,保存PCB重新设置规则,再进行BGA扇出,如图9-41所示。

图9-41 导出不带规则的ASC文件

4.铜皮绘制

PADS Router组件铜皮处理与PADS Layout组件操作类似,一般铜皮会在PADS Router中处理,再到PADS Layout内进行灌铜处理。

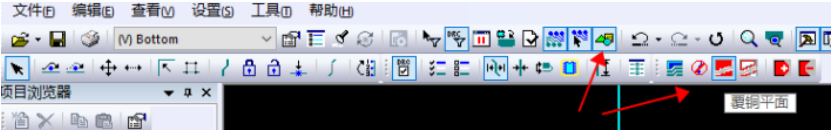

(1)单击“绘图操作”按钮,单击“覆铜平面”按钮,如图9-42所示。

图9-42 “覆铜平面”按钮界面

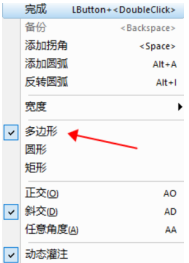

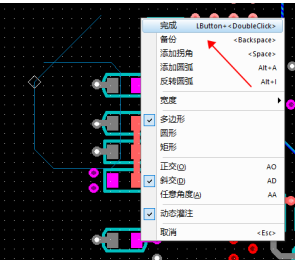

(2)在操作界面右击选择“多边形”项,并绘制铜皮形状,如图9-43所示。绘制完成后右击完成,绘制前注意设置好格点。

图9-43 绘制铜皮形状界面

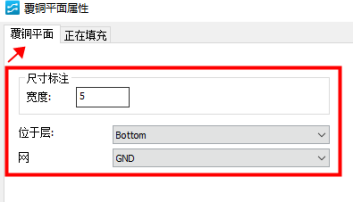

(3)在弹出的“覆铜平面属性”界面内的“覆铜平面”页填上铜皮线宽度,此宽度应不小于栅格设置时铜皮的宽度,否则为网格铜显示。“位于层”栏选择铜皮所在层,“网”栏选择铜皮所属网络,如图9-44所示。

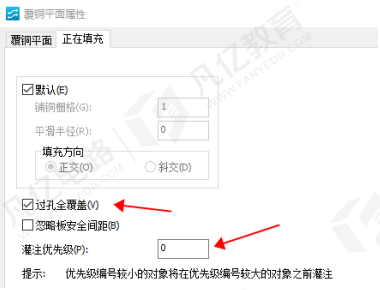

(4)在“正在填充”页勾选“过孔全覆盖”选项,“灌注优先级”栏设置好优先级别,数字越小级别越高,如图9-45所示。

图9-44 覆铜平面页设置 图9-45 正在填充页设置

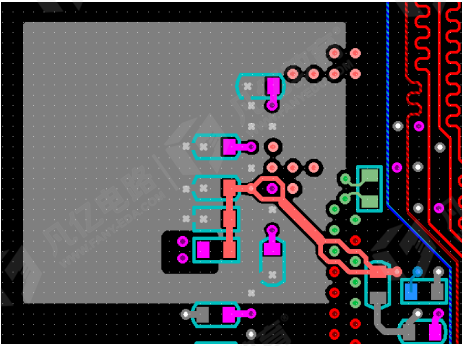

(5)绘制完成后,可使用无模命令“po”对铜皮进行显示,如图9-46所示。绘制铜皮时注意面积过小会导致灌铜失败,绘制时注意附近有没有禁布区域,禁布区域内铜皮会消除。

图9-46 铜皮显示效果

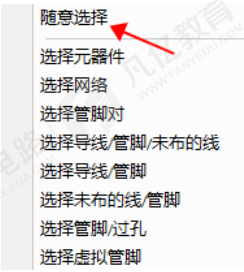

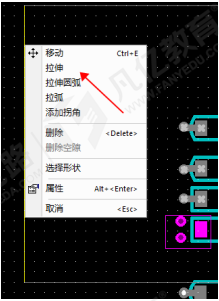

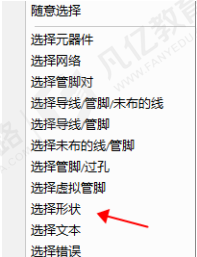

(6)切换到边缘显示模式时,右击选择“随意选择”命令,选中铜皮边缘右击,选择“拉伸”命令可对铜皮进行编辑,如图9-47所示。

图9-47 编辑铜皮1

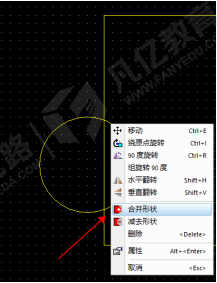

(7)若对铜皮形状不满意,可通过“合并形状”、“减去形状”功能编辑形状。在PCB内右击选择“选择形状”命令,在原有的铜皮附近绘制一个铜皮,通过此2个铜皮合并或者消除编辑铜皮,绘制好铜皮后,将需要合并或者消除的铜皮选中,右击选择“合并形状”命令,则会将2个铜皮合并为一个铜皮,如图9-48所示,合并时铜皮网络应保持一致。

图9-48 编辑铜皮2

5.差分信号处理

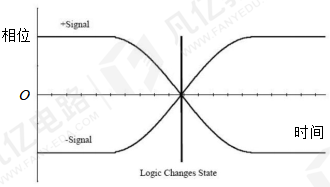

差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法,差分传输在这两根线上都传输信号,这两个信号的振幅相等,相位相差180℃,极性相反。在这两根线上传输的信号就是差分信号,如图9-49所示。

一般在PCB设计时,习惯的硬件命名上会在差分信号的信号名尾部加“+”和“-”或者“P”和“N”作为标识,大家可以通过命名来识别差分信号。常规的差分信号处理方法是:

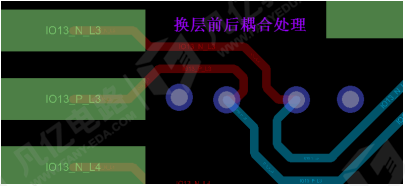

差分信号走线要耦合处理,就是2根信号线在PCB设计时是紧挨着耦合的,不允许分开走线,如图9-50所示。

图9-49 差分信号相位图示 图9-50 差分信号布线耦合处理参考图示

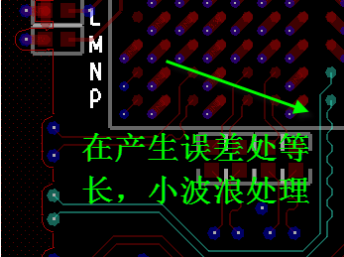

一对差分信号的2根信号线之间需要做等长处理,等长范围为5mil,等长不需要做到更小,有仿真验证,等长范围做到5mil以下并不能对信号质量有很大提升。等长处理的位置选择在产生长度误差的地方,等长需要做小波浪处理,如图9-51所示。

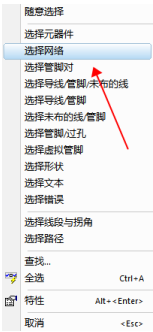

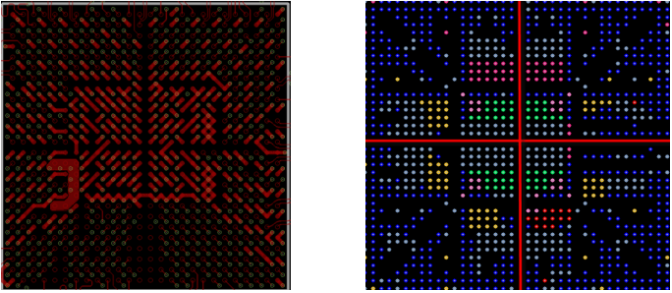

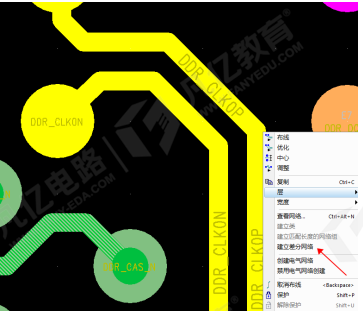

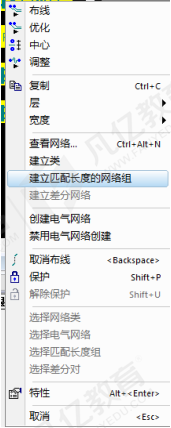

(1)通过原理图识别出差分信号,在PCB内右击选择“选择网络”,将一对差分网络选中右击选择“建立差分网络”,如图9-52所示。

图9-51 差分信号线小波浪处理参考图示 图9-52 建立差分网络

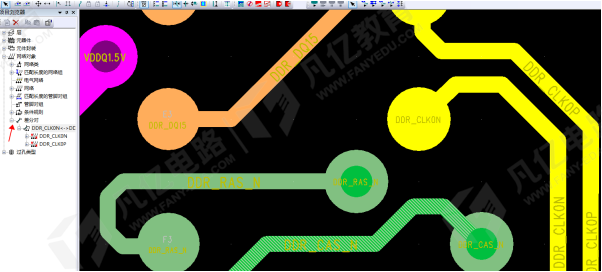

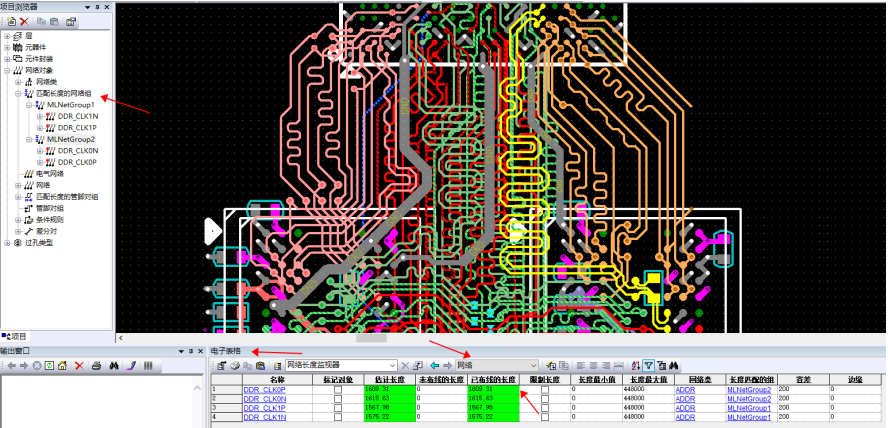

(2)查看项目浏览器中“网络对象”下的“差分对”元素,可以看到生成的差分对,如图9-53所示。

图9-53 差分对

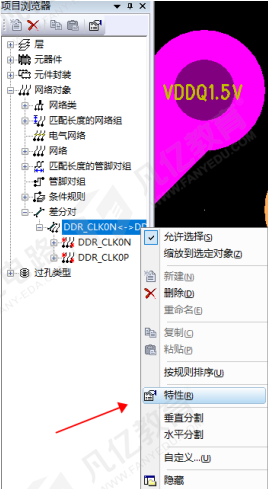

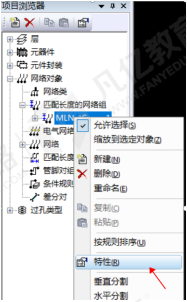

(3)创建好差分对,可对差分对进行规则设置。在“差分对”下选择创建的差分对名称,右击选择“特性”命令,如图9-54所示。

图9-54 选择差分对特性

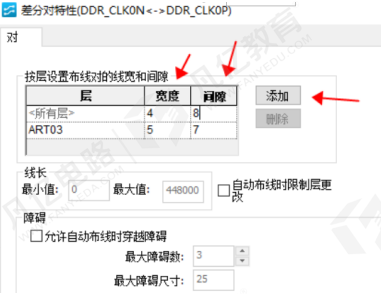

(4)在弹出的“差分对特性”页面进行差分对线宽线距值添加,若是多层项目设计,则可使用“添加”按钮对层规则进行添加,如图9-55所示。线宽与间隙值根据阻抗计算值进行设置。

图9-55 设置差分对特性

(5)执行交互式布线命令(快捷键F3)可进行差分对布线,如图9-56所示。在走线命令中可以通过右键进行一些特殊操作,如添加拐角,单独布线(快捷键Shift+Z)等,如图9-57所示。

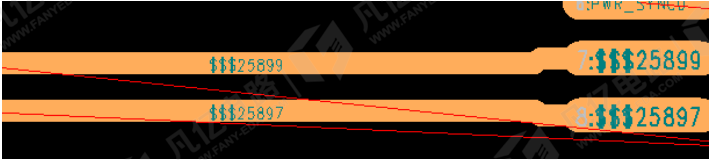

图9-56 差分对布线

(6)布线时遇到DRC会导致布线失败,且因拓扑情况,导致差分对信号间连接距离很近,但是不能直接连上,此时可切换到PADS Layout内进行拉通,再进行修线处理,修线时建议设置格点为0,以便使差分耦合布线。修差分对信号线时,可观察信号的保护带,正常情况下差分对信号与另一信号保护带是贴着的,若有空隙则证明差分对不耦合,需要修线处理,如图9-58所示。

图9-57 右键功能选项 图9-58 差分对耦合

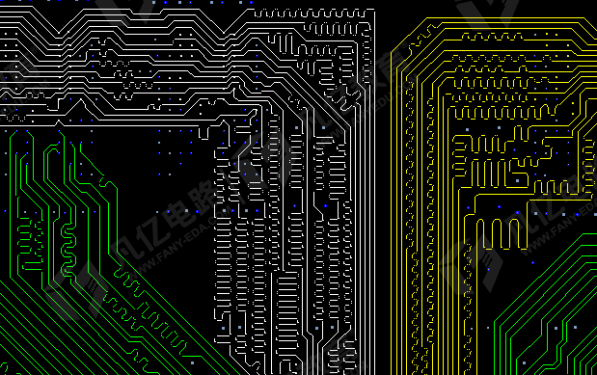

6.蛇形等长处理

在做PCB设计时,为了使某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是俗称的PCB信号等长处理,如图9-59所示。

图9-59 蛇形等长

一般做等长是为了满足系统对信号组的等时,即为了满足此组内信号的时序要满足系统要求。比如对于DDR,其数据信号每8位一组,做+/-25mil处理,如果此组信号等长没有在此公差范围内,信号线长度相差太大,会导致其相对延时较长,最终使DDR运行速率不高。但是做设计有时发现DDR器件等长没有做,其成品也可正常运行,并没产生影响,原因一般是系统软件对此信号做了延时处理,软件上做了时序控制。对于带状线来说,每1ps延时对应的走线长度是6mil左右,所以一般信号组长度每相差6mil,其总延时在1ps。一般做设计时等长并不用控制得太小,+/-10mil左右就已经很好了。+/-10mil 等长和+/-1mil 等长,在时间上的差异不超过 4ps,一般的IC信号裕量都不止4ps,所以做等长时没必要控制得过小,从而导致设计走线困难。差分信号等长是为了满足相位要求,一对差分信号相位相差180°,如果长度相差太大,会导致其相位偏移过大。设计上具体哪些信号需要进行蛇形等长处理,可查阅高速接口或者芯片模块的设计规范。

(1)首先设置匹配长度网络组,在PADS Router里面选中需要设置的多根网络(Ctrl+鼠标左键),鼠标右键在弹出的对话框选择“建立匹配长度网络组”命令,如图9-70所示。

图9-70 设置匹配长度网络组

(2)设置等长容差参数,即等长长度差范围。在项目浏览器中,选中“网络对象-匹配长度网络组”,右键打开菜单,选择“特性”命令,在“匹配长度组特性”下设置容差值,如图9-71所示。

图9-71 设置容差值

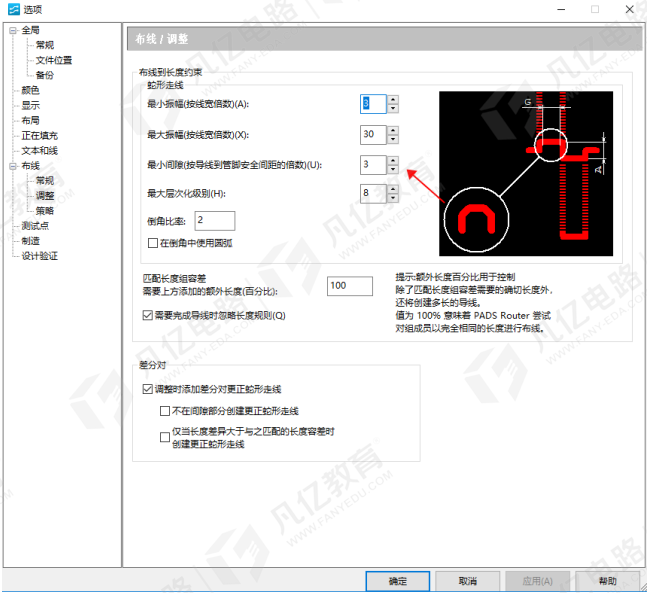

(3)执行菜单命令【工具】→【选项】,在弹出的“选项”对话框中的“布线/调整”标签页下设置蛇形走线的参数,如图9-72所示。最小间隙设置为3倍线宽,至少2倍以上,不能设置过小。

图9-72 设置间距

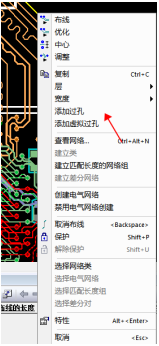

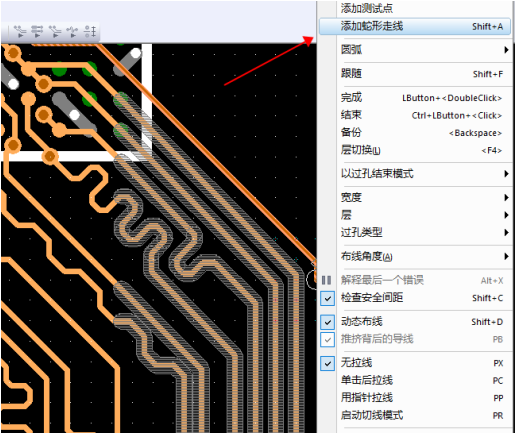

(4)设置完成后可进行等长处理,先将信号线连通,然后在需要进行等长的位置,删除一段信号线,按“F3”键,单击线头位置,拉线过程单击鼠标右键,然后选择“添加蛇形走线”命令(或者按组合快捷键“Shift+A”),如图9-73所示。

图9-73 添加蛇形走线

(5)等长过程中,注意设置好格点,等长布线时注意拉线控制好方向,歪了或者有DRC可能导致软件等长失败,要多操作几遍,不熟悉等长操作的或者空间不足会导致等长困难。

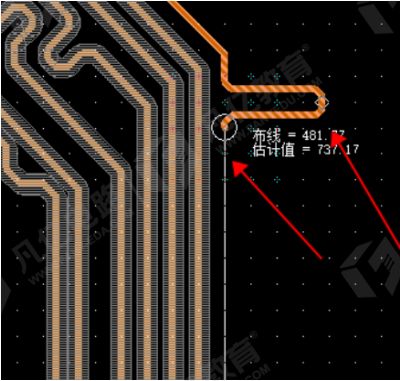

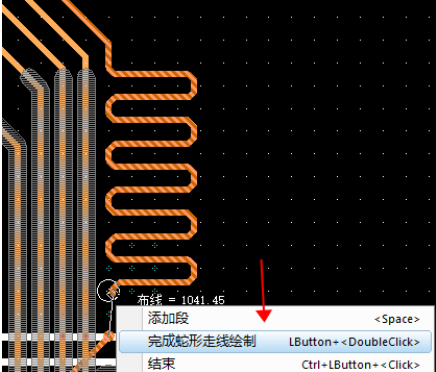

(6)执行添加蛇形走线后,软件会计算蛇形等长的形状,将鼠标往布线前方移动,会自动生成蛇形线,单击选择蛇形等长的最高位置,再单击最低位置,再向前移动,软件会自动生成移动方向的蛇形线,到结束位置单击,右击选择“完成蛇形走线绘制”命令,将信号连通,完成蛇形布线,如图9-74所示。

图9-74 蛇形走线

(7)执行菜单命令【查看】→【电子表格】,或者单击快捷栏表格快捷按键,如图9-75所示,可查看网络组各网络的布线长度,如图9-76所示,选择“网络”项,可查看建立了“匹配长度的网络组”的信号长度,此表格中“已布线的长度”为真实的长度,只需要关注这个值。可根据此值或者颜色提示判断等长情况,等长时注意将上下拉的信号长度先删除,等长完了再连通,以免产生误差。

图9-75 调用电子表格

图9-76 查看网络长度

黄色:已完成的布线长度比等长要求长度短。

绿色:布线长度在等长容差之内。

红色:布线长度超过等长要求长度。

扫码关注

扫码关注