- 全部

- 默认排序

华为OD招聘现需硬件工程师2名:岗位要求如下:1.电子、通讯相关专业本科或以上毕业;2.三年以上硬件研发工作经验,具有高速数字电路硬件设计优先;

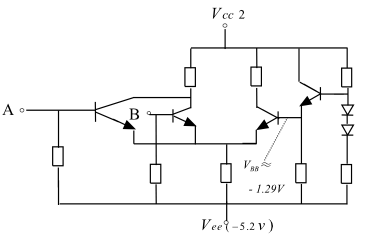

高速数字电路应用广泛,是电子工程师及小白需要重点学习并运用的电路,但有很多人就会很好奇高速数字电路种类那么多,有哪种?所以本文将搜集平台内容,分享常见的高速数字电路,希望对小伙伴们有所帮助。1、ECL(Emitter Coupled Log

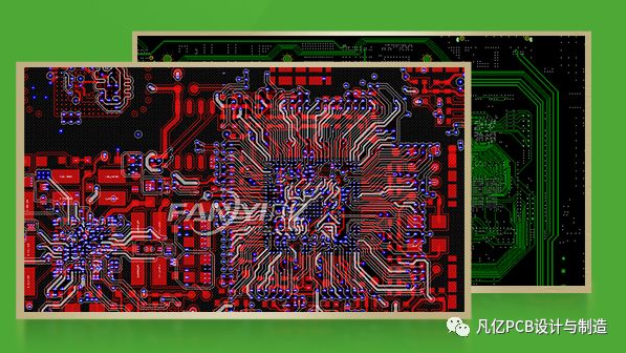

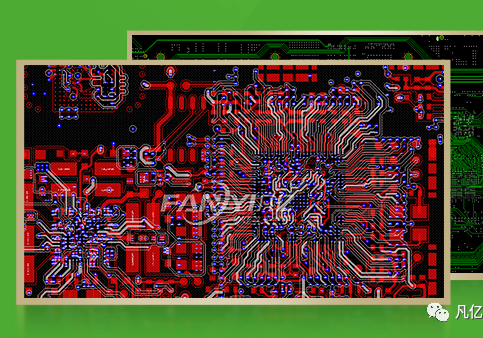

随着现代高速数字电路急速发展,差分信号传输已成为当代电子工程师必须掌握的重点技术之一,它可以有效抵消信号传输过程中的共模噪声,在差分信号传输中,如何正确匹配差分阻抗是至关重要的,所以本文将讨论如何在PCB布线阶段中正确匹配差分阻抗?在PCB

在PCB设计过程中,若是在电源平面或地平面的分割处理不当,很容易导致平面的不完整,信号走线时,其参考平面将出现在一个电源面跨接到另一个电源面,这种现象叫做信号跨分割。跨分割对低速信号影响不大,但在高速数字信号系统重影响很大,所以电子工程师该

现阶段许多公司仍然是让硬件工程师来进行PCB设计和方案开发,除开这些,硬件工程师还要做更多的专业工作,这样势必会使产品上市的时间大大延长。而且现在随着高速数字电子技术的发展,对高速PCB设计的要求也越高:信号完整性仿真分析、 时序分析, 单

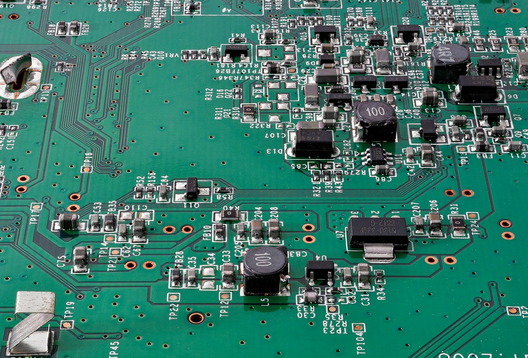

凡亿深圳pcb培训讲解PCB设计走线时注意事项总结如下: 1. 一般规则 1.1 PCB板上预划分数字、模拟、DAA信号布线区域。 1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。 1.3 高速数字信号走线尽量短。 1.4 敏感模拟信号走线尽量短。 1.5 合理分配电源和地。

提起信号完整性(SI)设计,很多人都不会陌生,信号完整性设计是确保电子系统可靠性和性能的关键因素。在高速数字系统和复杂电路设计中,信号完整性面临着诸多挑战,所以工程师需要注意很多地方,做好SI设计,那么需要注意哪些?在设计SI前,首先要思考

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

在高频电路中,串音可能是最难理解和预测的知识点,也是工程师最为头疼的设计难点,工程师在设计高频电路时必须采取措施尽量避免串音,以免影响到电路正常运行。要想避免串音,就必须了解串音是什么,如何产生。首先,当信号沿着印刷电路板的布线传播时,其电

现阶段许多公司仍然是让硬件工程师来进行PCB设计和方案开发,除开这些,硬件工程师还要做更多的专业工作,这样势必会使产品上市的时间大大延长。而且现在随着高速数字电子技术的发展,对高速PCB设计的要求也越高:信号完整性仿真分析、时序分析,单板和

扫码关注

扫码关注