- 全部

- 默认排序

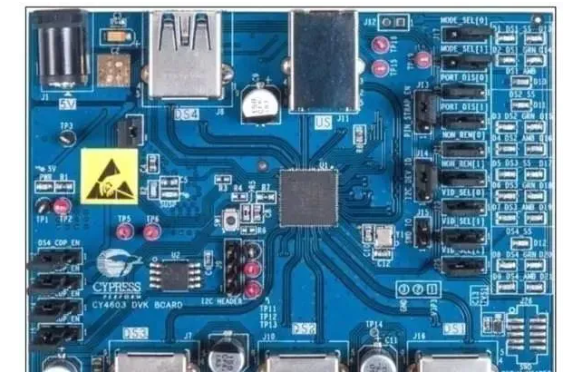

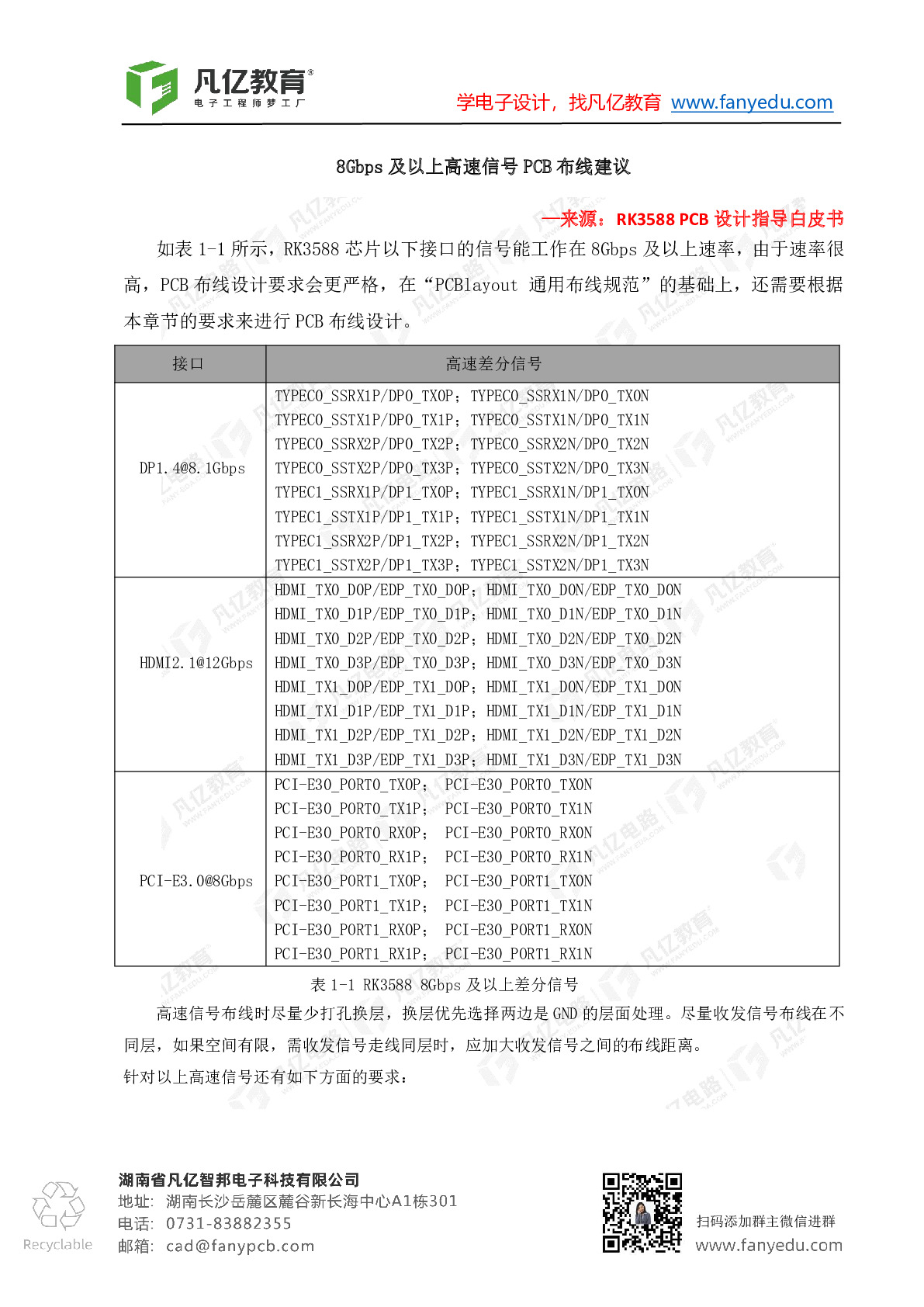

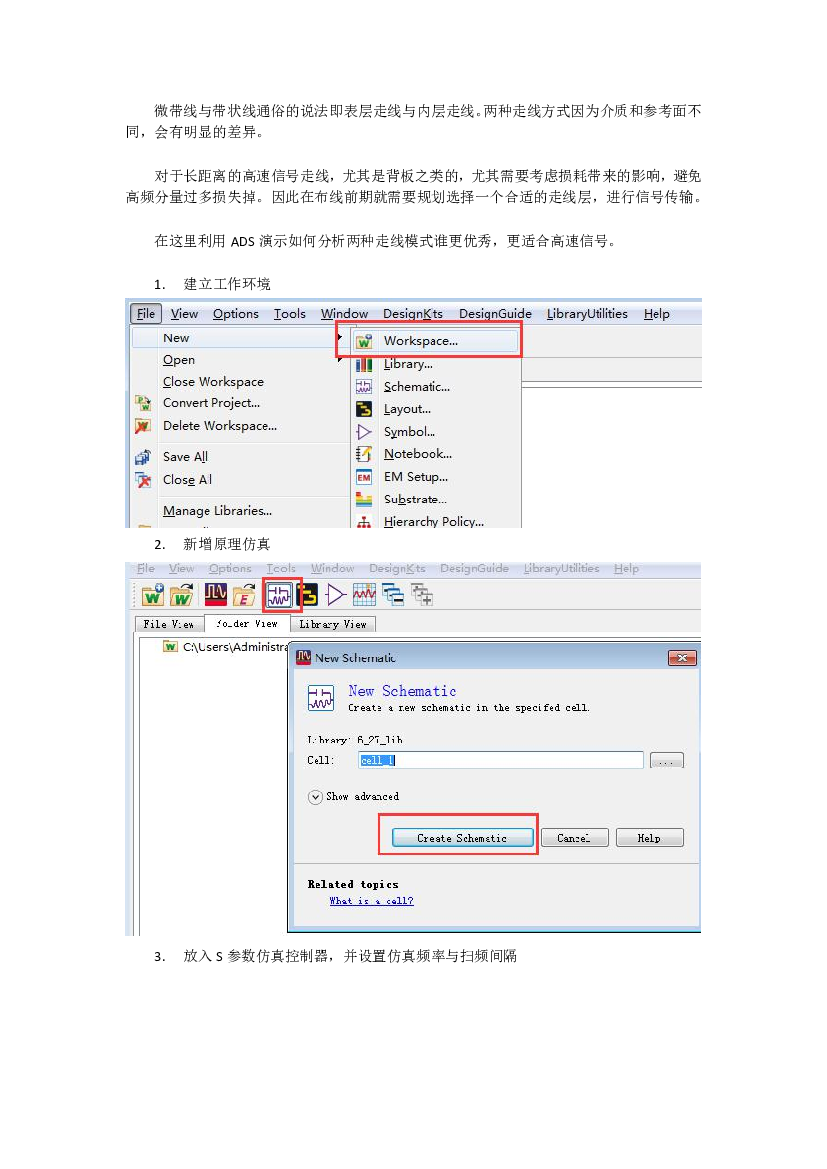

要点:1.高速PCB在设计中常见的问题;2.高速PCB的特殊材料要求;3.高速信号传输的特征和挑战4.高速PCB设计的原则和考虑因素5.PCB设计存在问题6.高速信号仿真分析工具有那些7.项目实例,高速PCB的信号完整性仿真办法和技巧

现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走线,要以45度角走线,并且会说走圆弧会比45度拐角更好。 事实是不是这样?PCB走线角度该怎样设置,是走45度好还是走圆弧好?90度直角走线到底行不行?

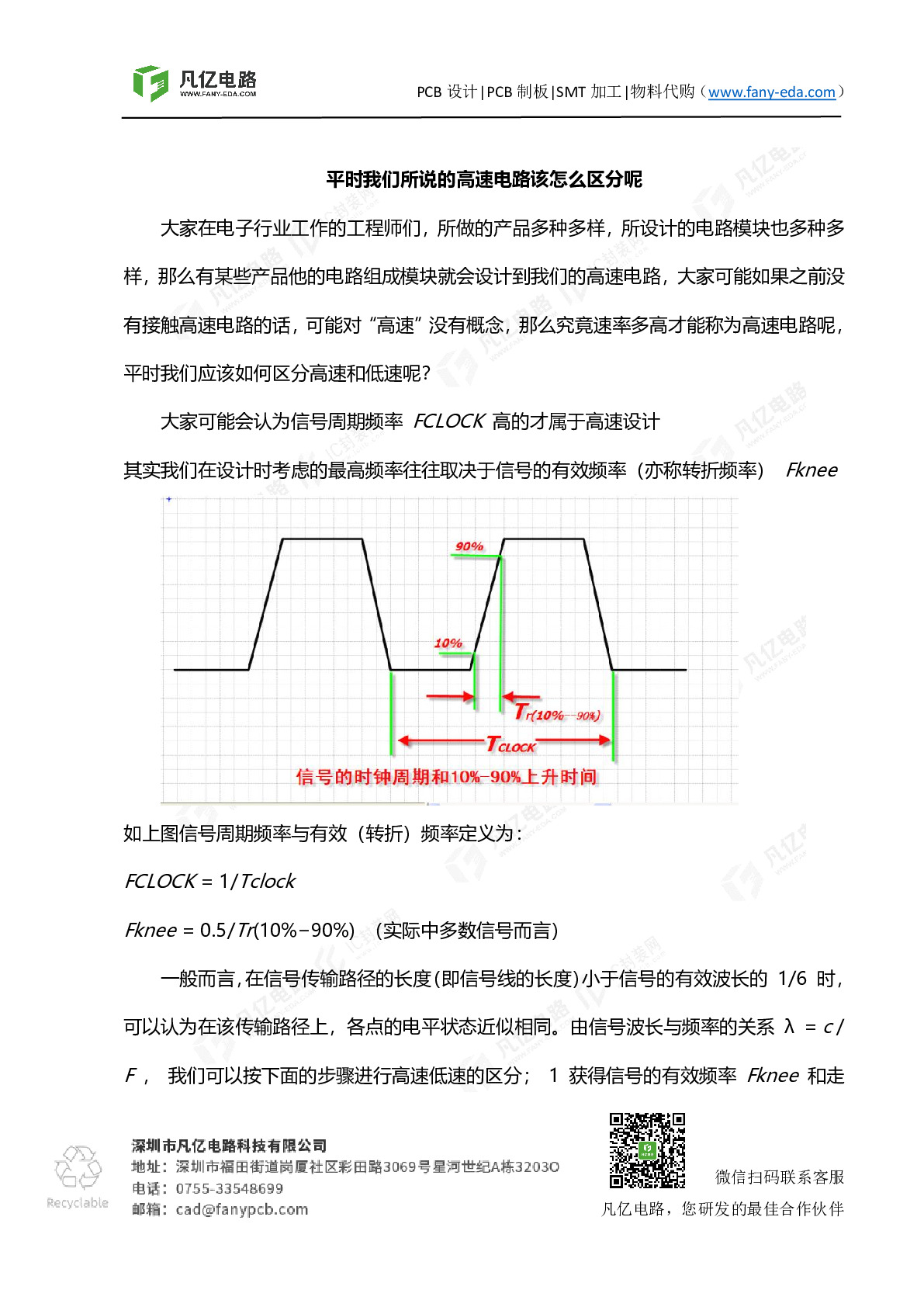

在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错。那么如何区分高速信号和普通信号呢?很多人觉得信号频率高的就是高速信号,实则不然。我们知道任何信号都可以由正弦信号的N次谐波来表示,而信号的最高频率或者信号带宽才是衡量信号是否是高速信号的标准。在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错

如何高效区分高速电路?

随着现代电子系统的告诉发展,对于高速信号的需求越来越高,高速电路设计愈发严格,因此很多电子工程师必须对高速电路有一定的了解及掌握,下面将谈谈如何区分高速电路,希望对小伙伴们有所帮助。1、信号频率和速率高速电路通常涉及高频率和高速率的信号传输

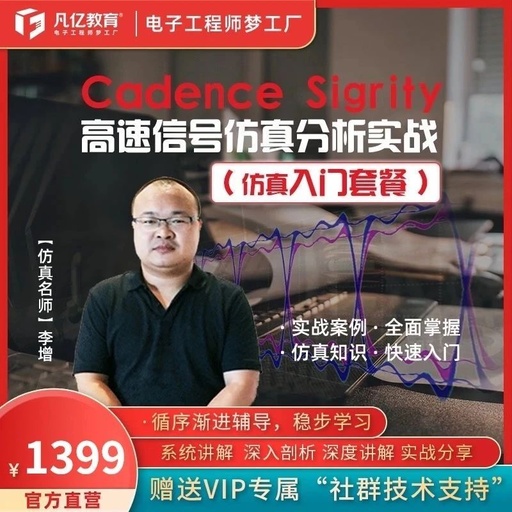

复制这段话到TaoBao打开即可见↓4.0 hi:/信O3t7XoWNUQP信 Cadence Sigrity高速信号仿真视频实战PCB仿真教程基础套餐 凡亿扫码添加助教小姐姐【备注:仿真基础】领取更多优惠复制这段话到TaoBao打开即可见↓4.0 hi:/信O3t7XoWNUQP信 Cadence

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

扫码关注

扫码关注