- 全部

- 默认排序

RF工程师在设计芯片和天线间的阻抗匹配时是否也遇到过这样的问题,根据数据手册的参数进行匹配设计,最后测试发现实际结果和手册的性能大相径庭,你是否考虑过为什么会出现这么大的差别?还有,匹配调试过程中不断的尝试不同的电容、电感,来回焊接元器件,这样的调试方法我们还能改善吗?一、理想的匹配通信系统的射频前

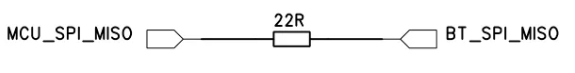

电阻串联大家应该在初中的课堂上就有接触,但那个时候只是比较浅显的,今天我就来讲一下电阻串联的作用。电阻串联常见作用第一个作用是:阻抗匹配。因为信号源的阻抗很低,跟信号线之间阻抗不匹配,串上一个电阻后,可以改善匹配情况,以减少反射,避免振荡等

详解阻抗匹配原理

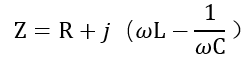

本文主要详解什么是阻抗匹配,首先介绍了输入及输出阻抗是什么,其次介绍了阻抗匹配的原理,最后阐述了阻抗匹配的应用领域,具体的跟随小编一起来了解一下吧。一、输入阻抗输入阻抗是指一个电路输入端的等效阻抗。在输入端上加上一个电压源U,测量输入端的电

射频设计中的阻抗

射频的黄金三角之一就是阻抗,我们在射频设计中,会经常与阻抗打交道,比如特征阻抗,负载阻抗,阻抗匹配等等。更多的时候,我们所设计的射频电路就是一个阻抗匹配的问题。我们今天一起来看一下有关阻抗的那些事儿。1阻抗谈到阻抗的概念,大家的第一影响就是

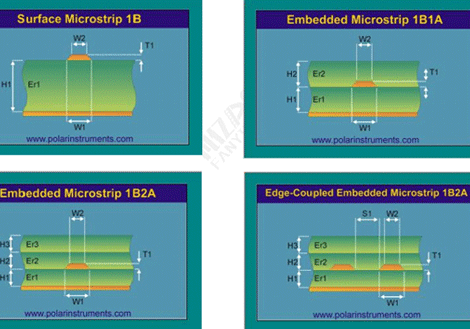

阻抗匹配和阻抗计算是高速PCB设计中的一个常见问题,也是小白初入高速PCB设计中最大的学习难点,今天我们将针对小白的学习难点,归纳总结,整理重点,为小白解惑。在高速PCB设计中阻抗匹配与否关系将联系到信号的质量优劣,而阻抗匹配是指在能量传输

谈谈阻抗匹配的理解

阻抗匹配(impedance matching)信号源内阻与所接传输线的特性阻抗大小相等且相位相同,或传输线的特性阻抗与所接负载阻抗的大小相等且相位相同,分别称为传输线的输入端或输出端处于阻抗匹配状态,简称为阻抗匹配。否则,便称为阻抗失配。有时也直接叫做匹配或失配。

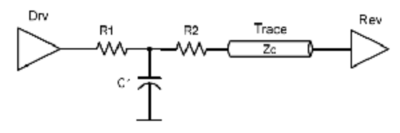

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:Ø 源端端接,接在信号源端或信号发送端的端接,一般与信号走线串接;Ø 终端端接,接在信号终端或信号接收端的端接,一般与信号走线并接。源端端接的优点是接供较慢的上升时间,减少反射量,产生更小的EMI,从而降低过冲,增加信号的传输质量。我们在PCB设计中处理源

答:随着信号传送速度迅猛的提高和高频电路的广泛应用,对印刷电路板也提出了更高的要求。印刷电路板提供的电路性能必须能够使信号在传输过程中不发生反射现象,信号保持完整,降低传输损耗,起到匹配阻抗的作用,这样才能得到完整、可靠、精确、无干扰、噪音的传输信号。阻抗匹配在高频设计中是很重要的,阻抗匹配与否关系到信号的质量优劣。而阻抗匹配的目的主要在于传输线上所有高频的微波信号皆能到达负载点,不会有信号反射回源点。因此,在有高频信号传输的PCB板中,特性阻抗的控制是尤为重要的。

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

端接电阻的认识和放置

端接电阻是用来实现阻抗匹配的。 什么是阻抗匹配,对于波形信号,在传输和使用的过程中会产生非线性阻抗,例如线路中存在电容或电感等非线性原件, 对于高频的信号不知道什么时候就会产生阻抗,此时就会影响信号的特性,频率或者能量都会改变,可以通过在电路中加入一种电阻控制电路的阻抗使之达到不影响信号,这种电阻就是端接电阻。端接电阻分为并行端接和串行端接两种

扫码关注

扫码关注