- 全部

- 默认排序

通信电源习题集 第1章 概述 一、 填空题 1. 通信电源是向通信设备提供所需交流电或______________的电能源。 2. 通信配电就是将通信电源系统的所有设备和设施,组合成一个完整的供电系统,合理地进行控制、分配、输送,满足______________供电的要求。

我有几个问题,想请教下。

我有几个问题,想请教下。fpga的,普通io是什么电平标准呢ecl.还是cml,lvds,那种标准。因为,实际高速设计时需要通过电平标准,来设计匹配电路但我没在手册上,看到过相关描述

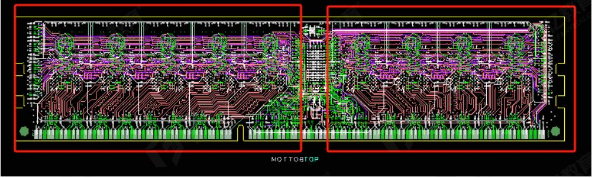

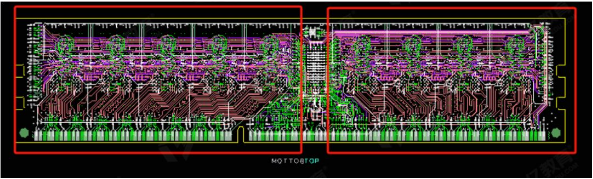

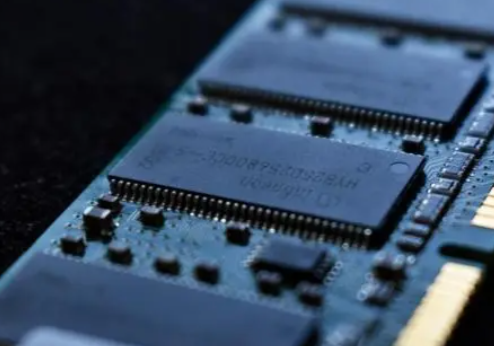

上次我们对不加端接电阻和加端接电阻之后的仿真结果做了分析之后我们得出在DDR采用菊花链拓扑结构的时候是需要加端接电阻的,这次我们看看DDR末端的端接电阻距离最后一片DDR远一点效果好一些还是近一点效果好一些。本次采用的案例依旧是我们上期的D

DDR采用菊花链拓扑结构时,由于信号传输线较长通常需要在DDR末端加上终端匹配电阻,端接的方式有很多,但是都是为了解决信号的反射问题,通常为了消除信号的反射可以在信号的源端或者终端进行解决,在源端处消除反射是采用电阻串联的方式,在终端处消除

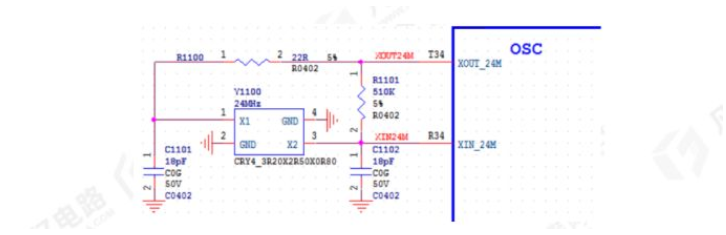

晶振可以说是集成电路的核心元件,一直以来是很多电子工程师在PCB Layout设计时的焦点所在,为了保证系统的优势最大化,晶振的Layout设计更是不能出错,本文将谈谈贴片晶振的Layout设计该如何做?1、匹配电容的摆放位置尽量靠近晶振;

时钟电路就是类似像时钟一样准确运动的震荡电路,任何工作都是依照时间顺序,那么产生这个时间的电路就是时钟电路,时钟电路一般是由晶体振荡器、晶振、控制芯片以及匹配电容组成,如图1所示。图1 时钟电路针对时钟电路PCB设计有以下注意事项:1、晶体

时钟电路就是类似像时钟一样准确运动的震荡电路,任何工作都是依照时间顺序,那么产生这个时间的电路就是时钟电路,时钟电路一般是由晶体振荡器、晶振、控制芯片以及匹配电容组成,如图1所示。图1 时钟电路针对时钟电路PCB设计有以下注意事项:1、晶体

零欧姆电阻与接地问题

0欧姆电阻作用1、在电路中没有任何功能,只是在PCB上为了调试方便或兼容设计等原因;2、可以做跳线用,如果某段线路不用,直接不贴该电阻即可(不影响外观);3;在匹配电路参数不确定的时候,以0欧姆代替,实际调试的时候,确定参数,再以具体数值的

端子压接标准及检验规范要求是电子电路中至关重要的一环,广泛应用于电气、通信、配电、自动化、航空航天等领域。为维护设备的正常运行和人身安全,制定端子压接标准及检验规范要求显得尤为重要。在这篇文章中,我们将介绍端子压接标准及检验规范要求的主要内

配电单元 (PDU) 有两种类型,基本型和智能型。虽然两者都可以为机架或机柜内的关键IT设备提供可靠的配电,但智能PDU提供了多种智能功能来帮助数据中心经理了解他们的电力基础设施。随着数据中心变得更加动态和复杂,智能PDU也变得更加普遍。什

扫码关注

扫码关注