- 全部

- 默认排序

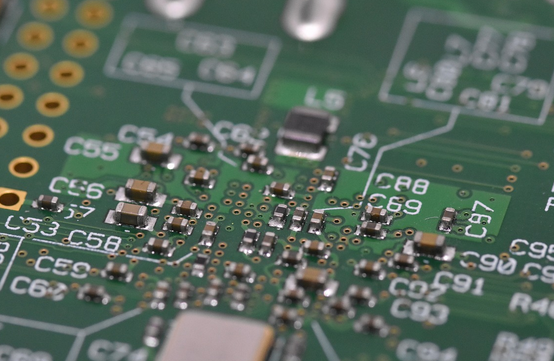

看了黄老师的教学视频后,从别的pcb文件导出了封装,调用打样之后,发现原来插件的2.54座子不是通孔,然后看了其他插件封装在原来的pcb文件上是插件,但是导出后变成不是插件了,请问怎么解决这个问题。下面是导出前,导出后,以及打样回来的图片

在电子制造行业,PCBA(印刷电路板组装)打样是一个关键而耗时的环节。对于工程师而言,减少打样时间不仅能提高工作效率,还能降低制造成本,加速产品上市。本文将探讨如何有效减少PCBA的打样时间。1、优化设计方案设计方案的合理性直接影响到打样时

我们在根据PCB板的要求,在规则编辑器里面加入了很多对应的规则。有比如:间距规则,线宽规则,短路等都是非常重要的电气规则规则,及其关乎到我们最后打样的关键。可是很多时候我们明明是在规则编辑器里面设置了规则的,为什么在我们规则之外的时候它竟然

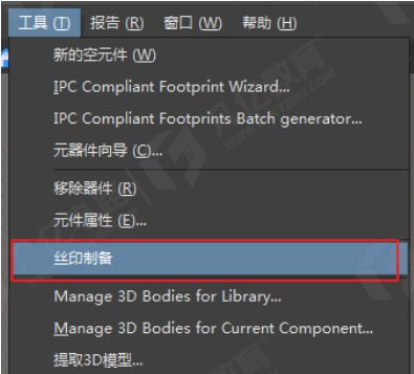

进行PCB设计时需要养成良好的设计习惯,才能保证后期的生产效果。例如整板上需要保证丝印跟阻焊的间距规则避免产生丝印重叠造成的PCB制造设计(DFM)问题。丝印重叠阻焊的影响有如下:1)PCB板后期打样,一般是以阻焊层优先,如果丝印跟焊盘重叠

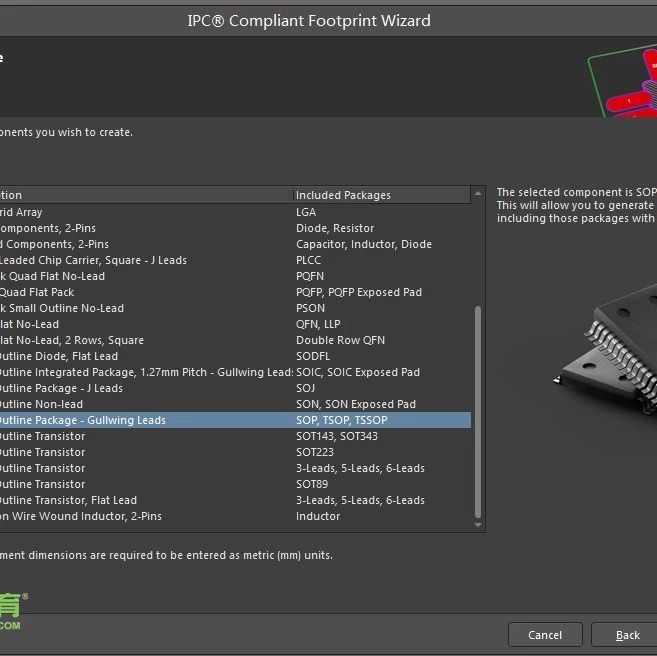

我们知道作为PCB设计工程师我们在进行PCB设计之前都需要进行PCB封装的创建,但是对于一些新手工程师对于创建的封装的精准数据无法进行判断,并且对一些焊盘的补偿参数不是很明白,导致自己做出的封装只能满足打样或者无法使用的囧状。针对这种情况其实我们Altium Designer考虑得比大家多多了,早早

扫码关注

扫码关注