- 全部

- 默认排序

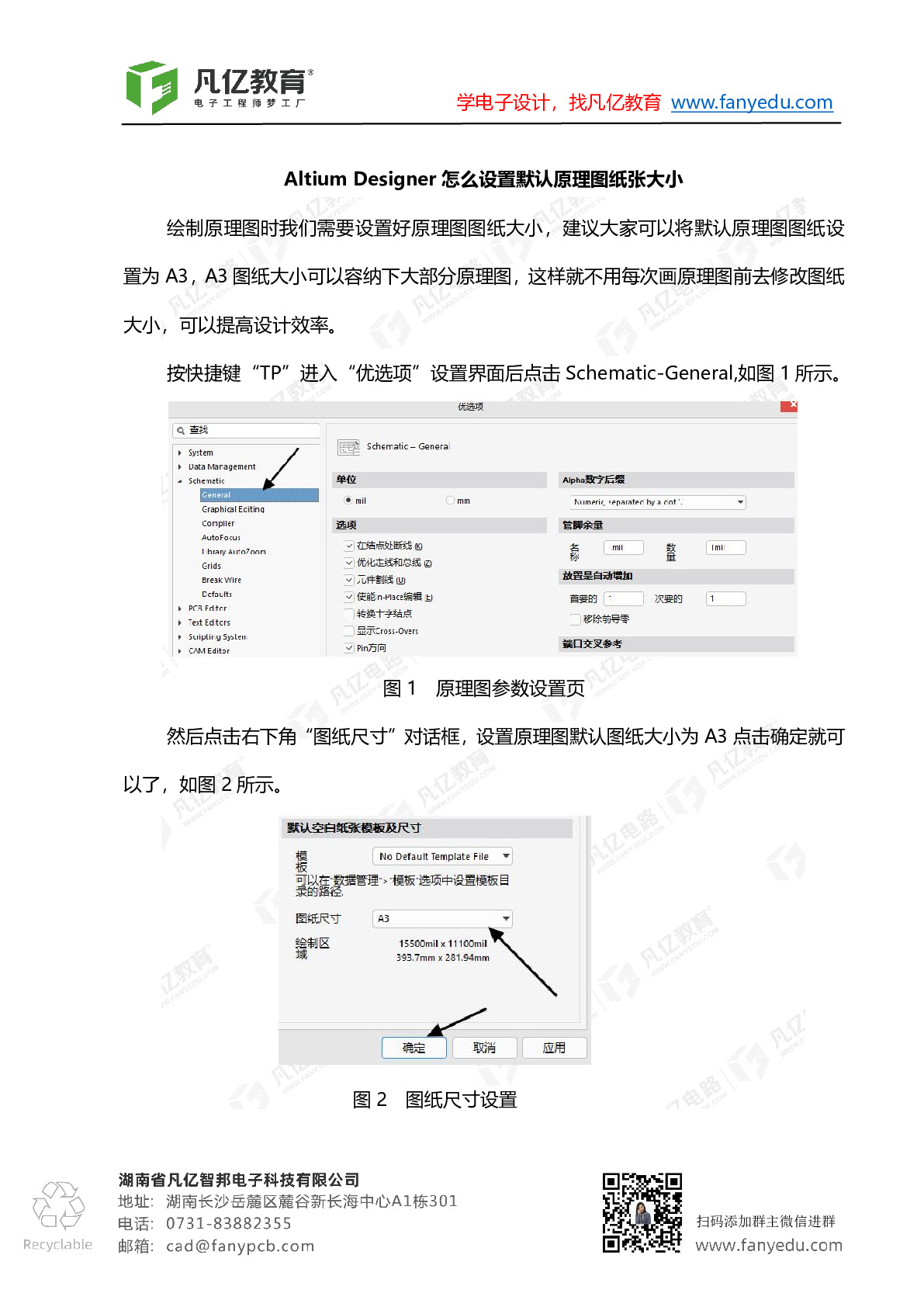

AD21!在画原理图时感觉A4图纸太小了,然后右击->原理图优先项===修改图纸大小(如设A3)。但是图纸是没有增大的,是什么原因?过去的protel,DXP,旧的AD09都没有此问题,当前电脑系统是W10;谁能解决

答:在绘制原理图时,放置出来的元器件,在图纸上都是显示器件的参数的,就是Vaule值,如图2-53所示,对于单个的属性参数,我们双击那个参数,会弹出Display Properties的对话框,如图2-54所示,在下面的对话框选择是否需要显示参数即可,Do Not Display表示都不显示;Value Only表示只显示Value值,也就是封装名称;Name and Value表示都显示。 图2-53 显示参数值原理图部分示意图 图2-54 显示参数设置

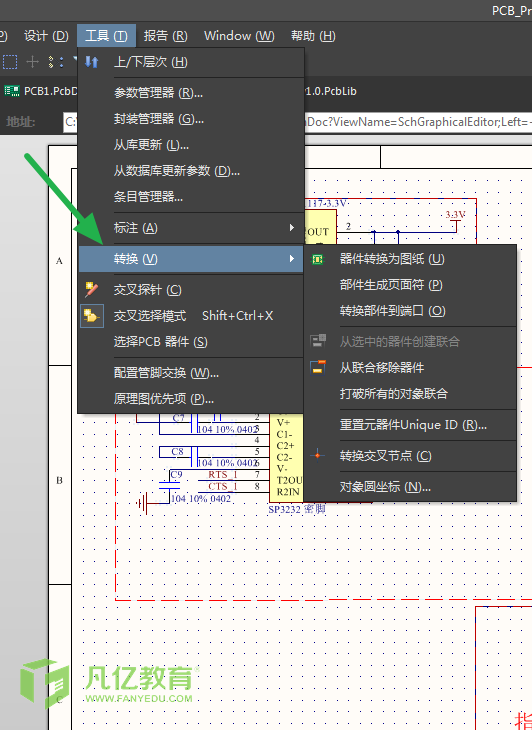

当我们在绘制原理图的时候,电路相同的模块可以进行复制粘贴,得到多个相同的原理图图纸,但是如果直接进行文件复制粘贴会出现ID相同的情况。这个unique ID在原理图和pcb中就是相当于这个元件的唯一身份许可证一样的,所以不可能两个元件之间相同。那么,在我们操作不当的时候造成ID相同怎么办呢?我们就需要对unique id进行复位。

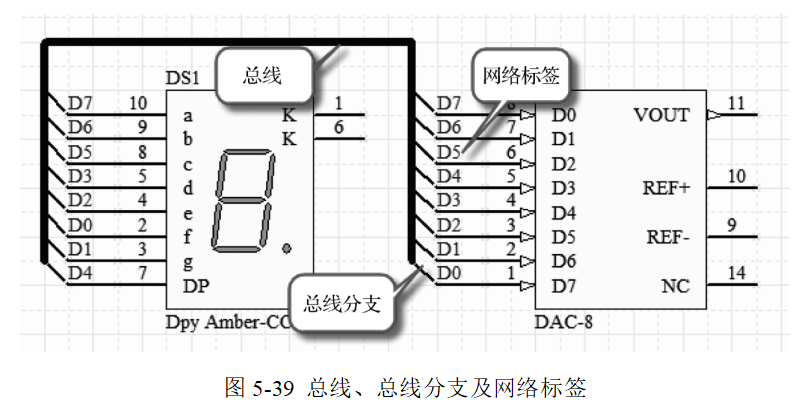

由于有时候使用到多图纸功能,这时需要考虑图纸页和图纸页间的线路连接。在单张图纸中,可以通过简单的网络标签(Net Label)来实现网络连接;而在多张图纸中,简单的网络标签无法满足连接要求。网络连接涉及的网络标识符(如表5-2所示)比较多,

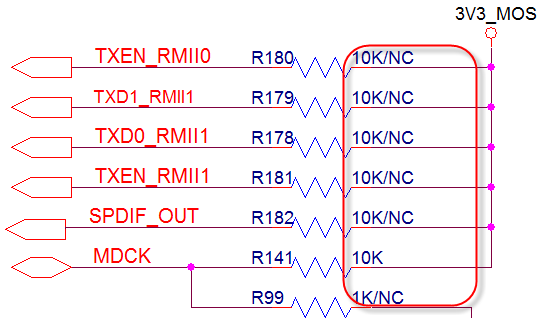

单纯的网络标签虽然可以表示图纸中相连的导线,但是由于连接位置的随意性,给工程人员分析图纸、查找相同的网络标签带来一定的困难。总线代表的是具有相同电气特性的一组导线,在具有相同电气特性的导线数目较多的情况下,可采用总线的方式,以方便识图。总线

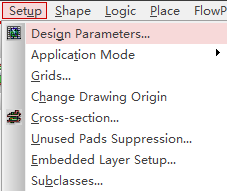

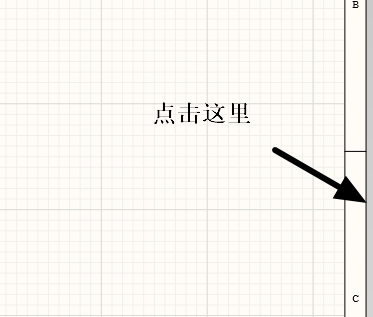

答:我们使用Allegro软件进行设计PCB图纸之前,需要对整个设计的参数进行设置,需要执行菜单命令Setup-Design Parameters,如图5-50所示:

原理图的元件材料清单(BOM)表主要用来整理一个电路或一个项目文件中的所有元件,它主要包括了元件的名称、数量、编号、封装、元件值等内容。这节视频就讲解了Logic中怎样输出元件材料清单(BOM)表,和其他报表的生成方式。

扫码关注

扫码关注