- 全部

- 默认排序

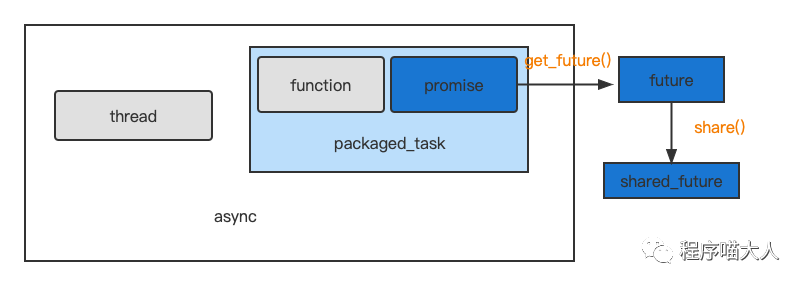

并发编程一般指多线程编程,C 11之后关于多线程编程有几个高级API:std::threadstd::futurestd::shared_futurestd::promisestd::packaged_taskstd::async可能很多人都搞不清楚它们之前有什么联系,可以直接看这张图:如果连它们

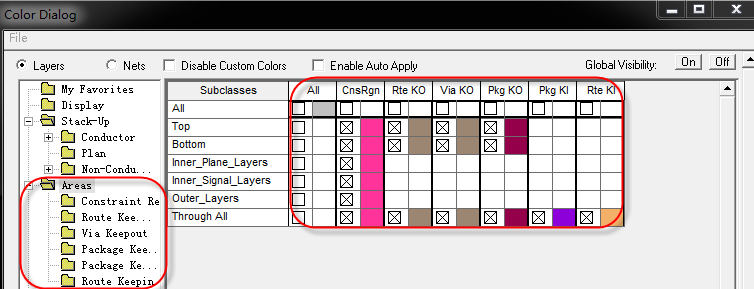

我们在进行PCB设计的时候,需要根据不同的PCB板结构以及一些电子产品的需求来进行各种不同区域的设计,包括允许布局区域设计、禁止布局区域设计。允许布线区域设计等等。在Allegro设计中,设置这些就在Areas,如图5-60所示。 图5-60 各类布局布线区域示意图Ø 在Allegro软件中有Route Keepout、Route Keepin、package Keepout、package Keepin、Via Keepout等多种类型的区域进行设置,对PCB工

在pcb布局和布线时,有时般出线路板的外形图的时候结构设计会考虑到电路板的装配等问题,会限制原件摆在某个区域里面,走线也限制在某个区域,所以就要设置package keepin和route keepin。

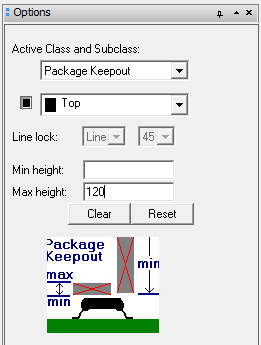

答:我们在进行一些复杂的PCB设计时,都会有很多结构限制,比如这里限高3MM等需求,为了辅助工程师们更好的进行设计,我们需要在PCB区域内绘制限高区域,并设置限高的参数,具体操作如下所示:第一步,在PCB板上绘制需要限高的区域,执行菜单命令Setup-Areas,在下拉菜单中选择package Keepout,如图5-66所示,显示器件禁布区。

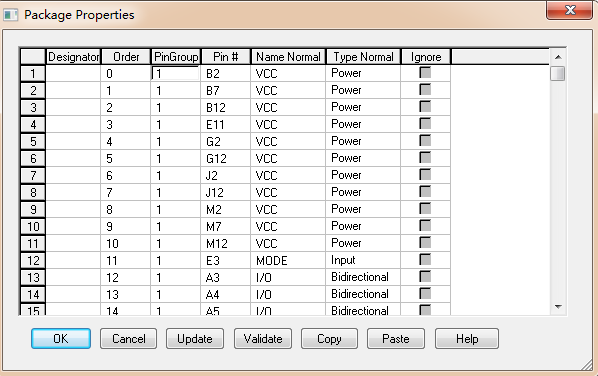

答:Pin Group这个属性是指可以交换的属性设置,我们删除这个属性的操作如下;第一步,打开库文件,点击菜单View→package,进入到整个器件的编辑属性,然后点击菜单Edit→Properties,或者按快捷键Ctrl+E,进入器件管脚属性编辑页面,如图2-92所示: 图2-92 编辑器件属性示意图第二步,在弹出的器件属性框找到Pin Group这一栏,Pin Group这一栏中定义了数值,数值相同的就是可以进行管脚交换的,如图2-93所示; 图2-93&n

17.4和17.2不一样吗?按照视频讲解的去做 按住ctrl 选中的管脚会拖动 而且我进入这个package里面这个package properties是无法点击的 也不像视频说的双击左键会出来 属性框

用Allegro软件里,每一个封装都有一个占地面积,一般是在package Geometry-Place_Bound_top层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。

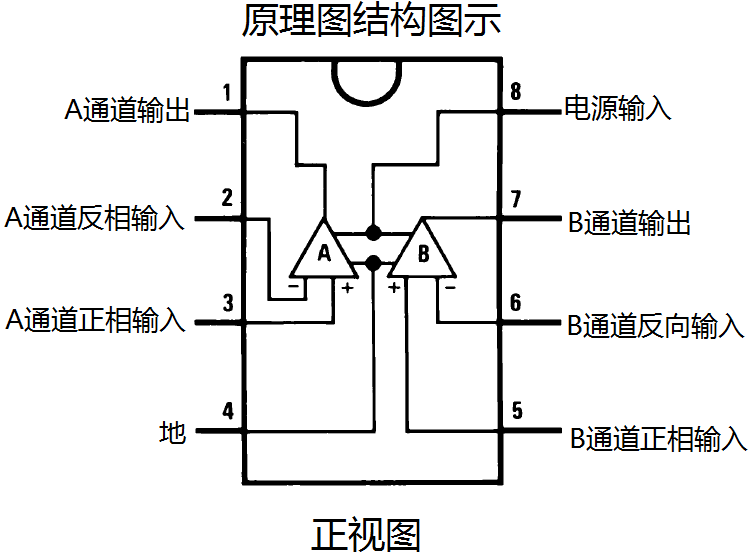

我们以LM358这个IC为例,讲解下Homogeneous类型元器件的创建方法,LM358的原理部分结构如图2-40所示,是由两个完全一样的放大器集成的, 图2-40 LM358原理部分构造示意图第一步,在olb文件单击鼠标右键,建立新的New Part,Name那一栏输入LM358,PCB封装那一栏可以先不填写,下面的Parts per pkg输入2个,由两部分组成,package Type选择Homogeneous,其它的按照系统默认即可,点击ok,如图2-41所示,&n

双列直插封装(dual in-line package)也称为DIP封装或DIP包装,简称为DIP或DIL,是一种集成电路的封装方式。DIP插件工艺是在SMT贴片工艺之后,是PCBA工艺中的一部分,DIP插件是指不能被机器贴装的大尺寸元器件

扫码关注

扫码关注