- 全部

- 默认排序

创建 FPGA 设计和维护 Vivado® 设计套件项目时,版本控制系统对于团队合作可能是一项具有挑战性的任务。工程师必须能跟踪设计变更,完整地从 hdl 或 TCL 源代码再现项目并交付特定的项目状态。Vivado 工具非常适用于这类工作

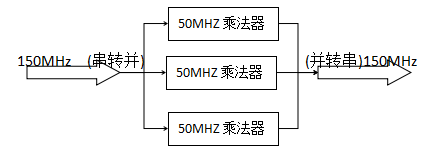

一、逻辑设计(1)组合逻辑设计下面是一些用Verilog进行组合逻辑设计时的一些注意事项:①组合逻辑可以得到两种常用的RTL 级描述方式。第一种是always 模块的触发事件为电平敏感信号列表;第二种就是用assign 关键字描述的数据流赋值语句。②always 模块的敏感表为电平敏感信号的电路可几

组合逻辑电路设计,在任何特定时间只能在输入的时间取决于输出,电路的原始状态无关。“也就是说,组合逻辑电路输出电路的历史地位并不重要,电路不包括存储单元。组合逻辑表达方法有三种:真值表,逻辑表达式和电路原理图。在veriloghdl描述组合逻辑电路中,与真值表对应的是用户自定义原语;而与电路原理图相对应的是门级建模,有个绰号又叫结构化描述;与逻辑表达式相对应的则称为行为描述。

很多萌新小白初入FPGA领域,无法确定自己的学习路线,也经常走弯路,耽误时间浪费精力,为了帮助小伙伴更好地确定自己的学习路线,轻装上阵学习FPGA,今天这篇文搜集了多位技术大牛的学习方法,归纳总结其特点,希望对小伙伴们有所帮助。需要注意的是

FPGA在逻辑芯片项目工程中是常见的,很多FPGA在项目中基本上都是以hdl代码来设计逻辑电路,但很多小白编写的hdl代码基本上都是不符合需求,费时费力,所以如何快速判断hdl代码是可行的?任何符合hdl语法标准的代码都是对硬件行为的一种描

扫码关注

扫码关注