- 全部

- 默认排序

WiFi6 MiniPCIE Module 2T2R2×2.4GHz 2x5GHzDR 7915https://www.wallystech.com/Network_Card/DR7915-wifi6-MT7915-MT7975-2T2R-

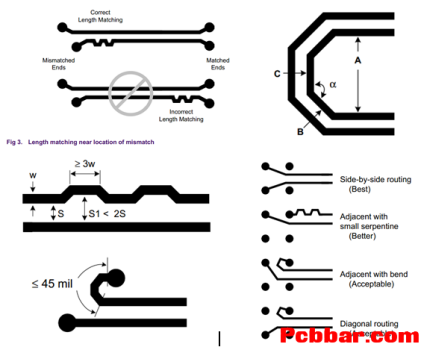

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

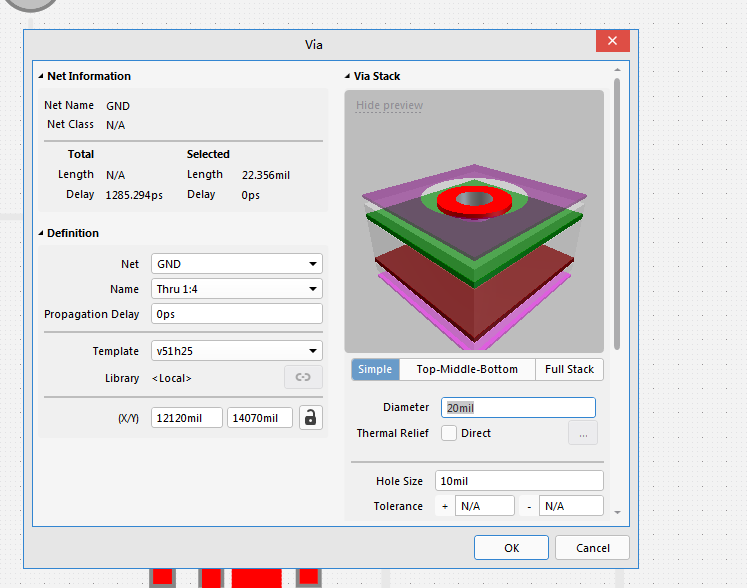

有时候为了为了增大内层的敷铜面积,特别是BGA区域,尤其在高速串行总线日益广泛的今天,无论是PCIE,SATA串行总线,还是GTX,XAUI,SRIO等串行总线,都需要考虑走线的阻抗连续性及损耗控制,而对于阻抗控制,主要是通过减少走线及过孔中的STUB效应对内层过孔进行削盘处理。

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

扫码关注

扫码关注