- 全部

- 默认排序

FPGA(现场可编程门阵列)作为可编程逻辑设备,一直广泛应用在各种数字系统设计,而JTAG接口是其中最常用的调试/编程接口,它的好坏将直接影响到FPGA的性能和可靠性。因此要对JTAG进行诊断和测试,以防止FPGA出故障,那么如何做?1、J

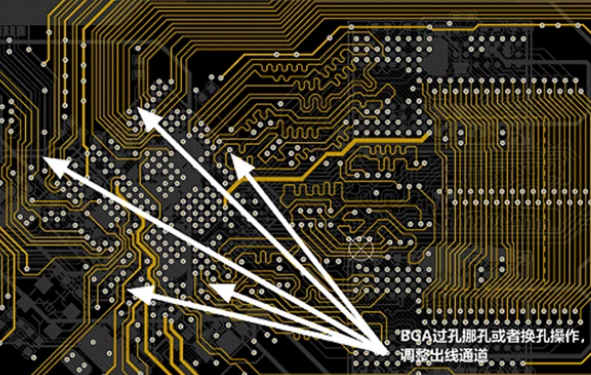

FPGA管脚调整是FPGA设计中的重要技术环节,主要涉及到FPGA芯片的输入输出管脚与外部硬件连接,确保信号传输的准确性和稳定性,工程师经常需要根据具体的应用需求来调整FPGA管脚配置,以此适配外部电路和信号接口,那么如何做?1、管脚规划在

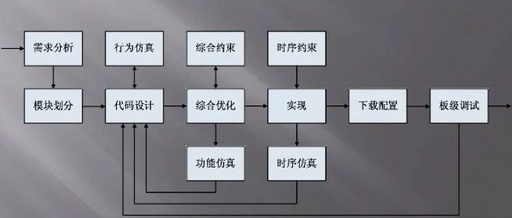

FPGA工程师所需掌握的基本技能FPGA的起源和发展 1985年Xilinx发布了全球首款FPGA芯片——XC2064。在当时那个年代,PC机才刚走出硅谷的实验室进入商业市场,因特网还只是科学家和政府机构通信的神秘链路,无线电话还像砖头一样笨重。FPGA芯片在当时似乎并没有什么用武之地。 早期的F

FPGA是一种功能强大的可编程逻辑器件,广泛应用在数字电路设计、信号处理、无线通信等多领域,自然也就成为电子工程师的关键技能之一,若是不合理使用FPGA,极有可能导致FPGA设计不稳定、延迟大、时序崩溃等问题,所以下面将聊聊FPGA设计中的

对FPGA工程师来说,可靠性设计是极其重要的,若是没处理好FGPA的触发器,没有满足特定的时序关系,导致FPGA电路不可靠,极有可能产生亚稳态问题,很容易打乱设计步伐,因此,了解FPGA设计的时钟域和亚稳态是很有必要的。一般来说,亚稳态意味

小伙伴们在学习FPGA时,最怕遇到同步时序电路设计,然而作为FPGA主要电路,同步时序电路试验频率居高不下,所以今天讲讲一些技巧,如如何实现同步时序电路的延时?如何实现RAM/ROM/CAM?1、FPGA设计中如何实现同步时序电路的延时?首

在FPGA设计时,我们总会遇到各种各样的设计难题,并发愁如何解决,所以小编将搜集网络上九个小白最头疼的FPGA设计问题,并进行回答,希望对小白有所帮助。1、如何控制XST插入buffer?①用buffer_type约束,具体使用方法在XST

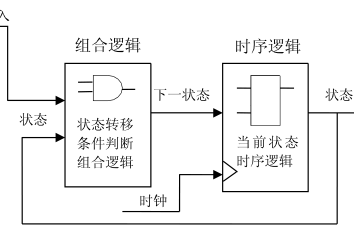

在FPGA设计里,状态机的设计是最为重要的环节之一。很多FPGA系统里的运行成功基本上和状态机设计相关,毫不夸张地说,FPGA系统的成功,其中一半归于状态机。所以我们该如何做好状态机?一般来说,工程师在状态机的设计中基本采用两段式写法(2个

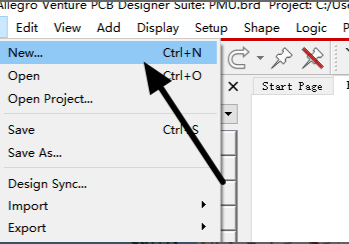

Cadence是一个大型的EDA软件,它几乎可以完成电子设计的方方面面,例如ASIC设计,FPGA设计和PCB板设计。Cadence包含的工具比较多,几乎是包含了EDA设计的全部,下面就介绍Cadence如何新建PCB。打开PCB Edit

扫码关注

扫码关注

![电子设计:云源软件安装及程序下载[零基础学FPGA设计-理解硬件编程思想]](https://api.fanyedu.com/uploads/image/56/f26c7093f8fcbe3907793cac815396.png)