- 全部

- 默认排序

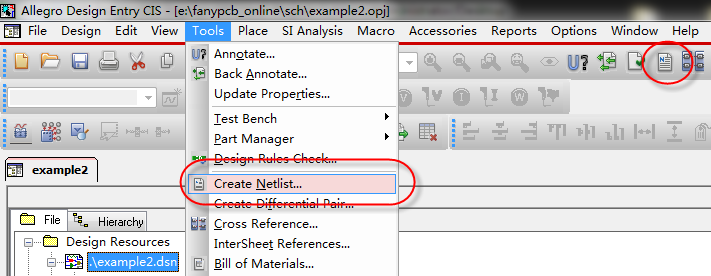

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

Access violation at address 29ECAFCA in module 'ADVPCB.dll'. Read of address 01DBB011 at 29ECAFCA. 画差分线出现这个问题怎么办,百度上的方法不好用

请问这种重新安装了也是这样,是显示已经破解成功了呀,或者有偿远程协助下

altlum designer 导dxf文档出现如下ErrorAccess violation at address 000000018F4B058F inmodule ‘LoadDXF.dll’,Read of address FFFFFFFFFFFFFFFF

扫码关注

扫码关注