- 全部

- 默认排序

同步电路是常见的电子电路之一,也是电子人才最头痛的电路学习难点之一,很多人在面对同步电路的时序约束和附加约束等等内容都会感到头疼,所以今天为帮助小伙伴们更好地理解,今天将换种方式聊聊同步电路的时序约束和附加约束?1、时序约束时序约束主要包括

华为同步电路设计规范

在同步电路中,触发器和亚稳态一直以来是电子小白的学习难点,学完同步电路后很多小白都不理解亚稳态是什么?为什么两级触发器可以防止亚稳态传播,所以今天来回答这些问题,希望对小伙伴们有所帮助。一般来说,亚稳态是指触发器无法在某个规定的时间内达到可

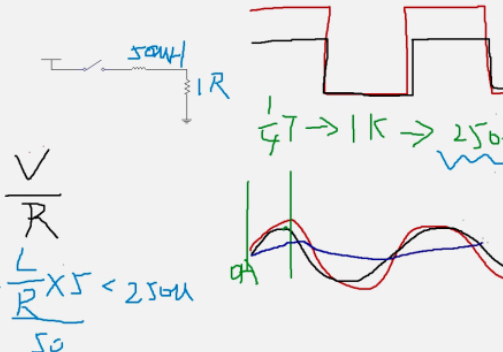

若是要了解触发器的建立时间和保持时间,必然离不开时序设计,而时序设计也同样离不开建立时间和保持时间,那么针对触发器的时序设计,我们来聊聊触发器的建立时间和保持时间吧。一般来说,时序设计的实质是满足每一个触发器的建立/保持时间的要求,而建立时

在设计数字电路时,电子工程师一般都要计算最高速度(最快时钟频率)和流水线,确保系统正常运行,对于优秀的工程师来说是轻而易举的事情,但对刚初入电子领域的小白来说是很难设计,那么该如何来设计最快时钟频率和流水线?同步电路的速度是指同步系统时钟的

同步电路和异步电路是常见的电子电路两大类,但由于小白经常将同步电路和异步电路混为一谈,导致在电路设计或面试过程中出错,所以了解同步电路和异步电路是很有必要的,接下来看看吧。1、同步电路和异步电路的区别及联系异步电路主要是组合逻辑电路,用于产

小白在设计数字电路,如同步/异步时序电路时常常会碰到毛刺或者亚稳态的问题,但很多小白对亚稳态问题措手不及,经常搞错电路导致系统崩溃,所以本文将归纳总结,分析数字电路中的亚稳态。在同步电路或异步电路中,如果触发器的setup时间或hold时间

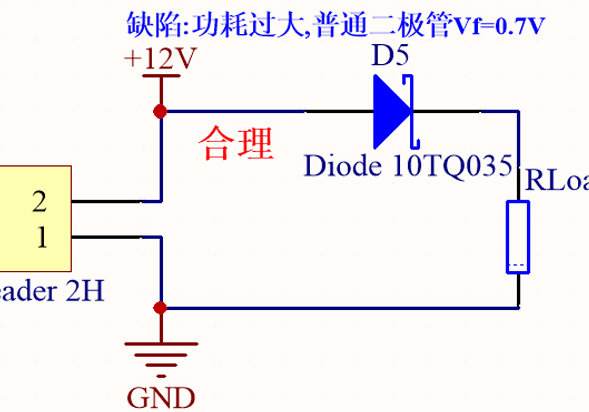

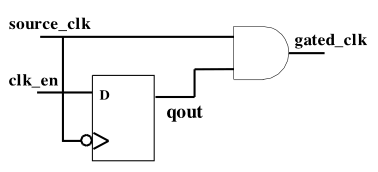

一般来说,很多工程设计都是通过同步时序电路来完成整个系统的设计,由于时钟的特点,时钟在同步电路设计中具有非常重要的作用。目前在电路设计中常见的是种类型主要分为全局时钟、内部逻辑时钟和门控时钟。1、全局时钟全局时钟即同步时钟,它是通过FPGA

同步电路是数字电路中常见的电路设计方法之一,但部分小白对该类电路不甚了解,甚至遇见该类设计是惘然无措,所以本文将重点分析同步电路的设计准则,并分享电路设计的优点。同步电路是指所有电路在同一个公共时钟的上升沿或下降沿的触发下同步地工作。但在实

全站最新内容推荐

- 1LED驱动模块RSC6218A 5W-18W迷你高效驱动电源应用-REASUNOS(瑞森半导体)

- 2从零开始成为电子大佬,第一步先识读电源!

- 3IEEE 1588 四通道/八通道系统同步器:8A34001E-000AJG、8A34002E-000NLG、8A34003E-000NBG(器件)

- 4光电器件故障了,如何排除维护?

- 5走进电子元器件,了解热继电器

- 6搞电子设计的人,转行能干什么?

- 7Solder Mask和Paste Mask有哪些不同?

- 8PCB板制造技术水平的标志如何看?

- 9雷军招人:为中国汽车工业全面崛起做贡献!

- 10单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

扫码关注

扫码关注