很多工程师在进行IC设计时都会选择FPGA来验证设计,而不是仿真模拟,这是因为与仿真相比,FPGA检查设计的效率高得多,当然大多数芯片开发中,都会选择FPGA原型机验证与RTL仿真结合起来。所以今天就聊聊基于FPGA的验证分析。

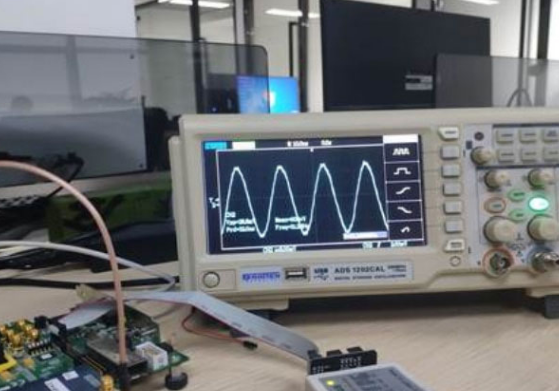

在FPGA的验证环节时,可将待测信号引到FPGA的引脚。采用示波器实时观测信号波形,此外,现在的FPGA实现工具一般都提供了通过计算机观察FPGA内部信号的功能,其远离是:通过JTAG口,将感兴趣的辛哈波形实时传送到计算机上,如Xilinx的chipscope就具备该功能。在引脚比较缺乏的场合下,这种方法是非常有用的。

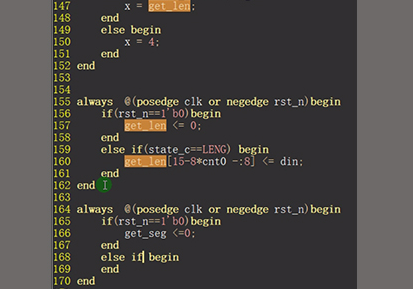

用FPGA进行验证的大致步骤具体如下:

①新建工程文件,读入设计文件;

②建立引脚定义文件及始终定义文件;

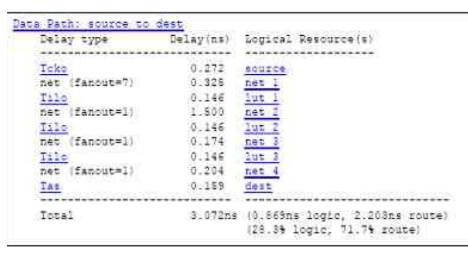

③给出综合约束和布局布线约束;

④综合,布局布线;

⑤生成下载文件,并将其下载到FPGA中;

⑥进行调试。

说明:如果专门针对FPGA进行设计,工程师必须先了解FPGA与ASIC的差异及联系,尽量采用与ASIC设计不同的设计风格。如:

在FOGA中,寄存器资源比较多,要尽量采用像one hot的编码方式,并尽量采用retiming/pipeline降低关键路径延时。

FPGA中连线延时较大;

FPGA提供了乘法器等IP实现,甚至还提供了嵌入式处理器。

FPGA的设计自由度低于ASIC。

常用的FPGA综合工具是Synplicity公司的Synplify,此外,Xilinx与Altera也提供了自己的综合和布局布线工具。

扫码关注

扫码关注

![电子设计:窗函数法FIR滤波器设计[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/6c/5f9bcf7016dbc3fd8579bfd7148121.png)