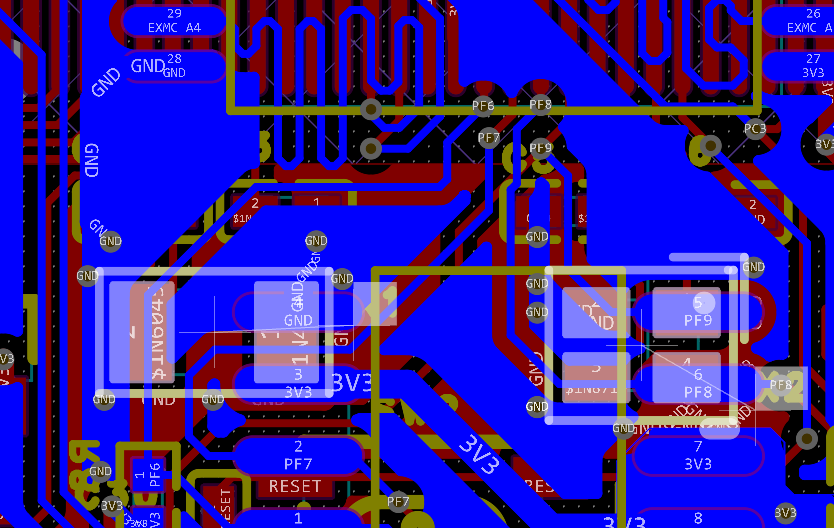

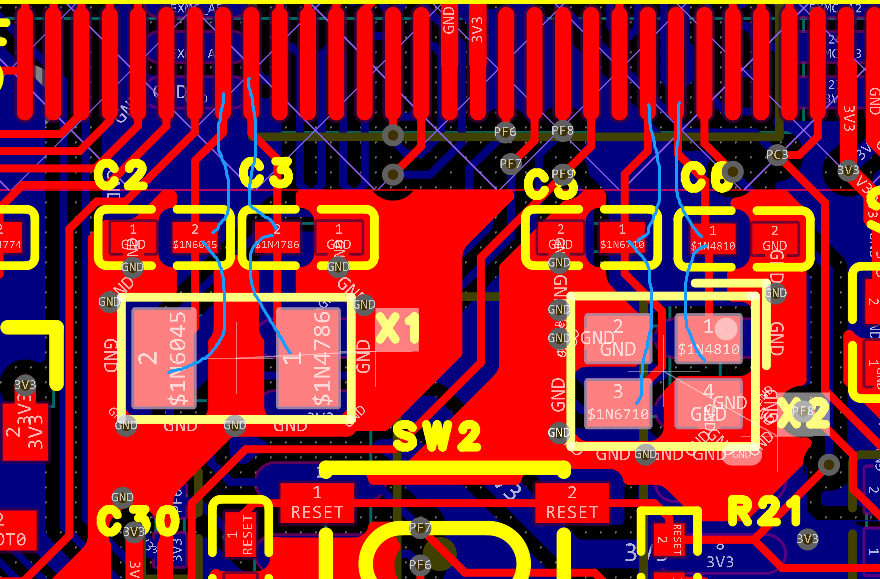

晶振下面尽量不要走线

2.晶振需要走类差分形式

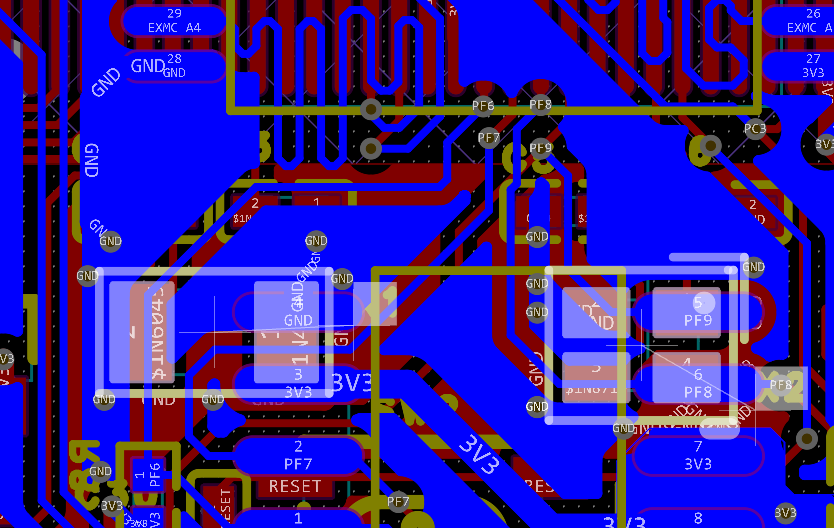

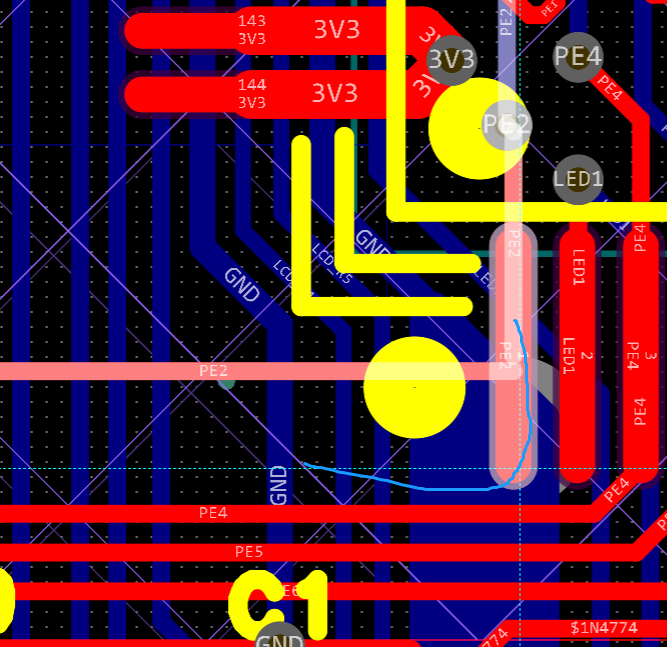

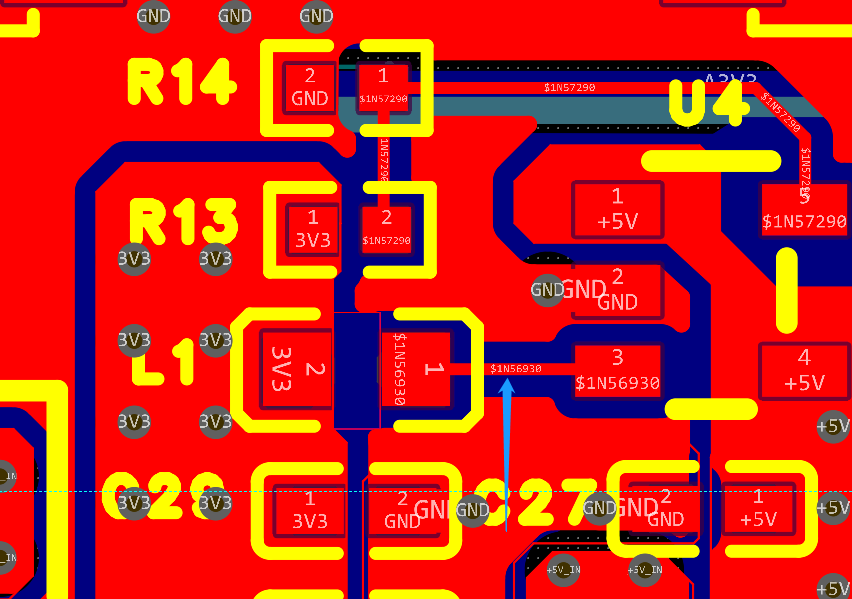

3.电源的输入输出需要铺铜处理,铺铜宽度需要满足电源电流大小

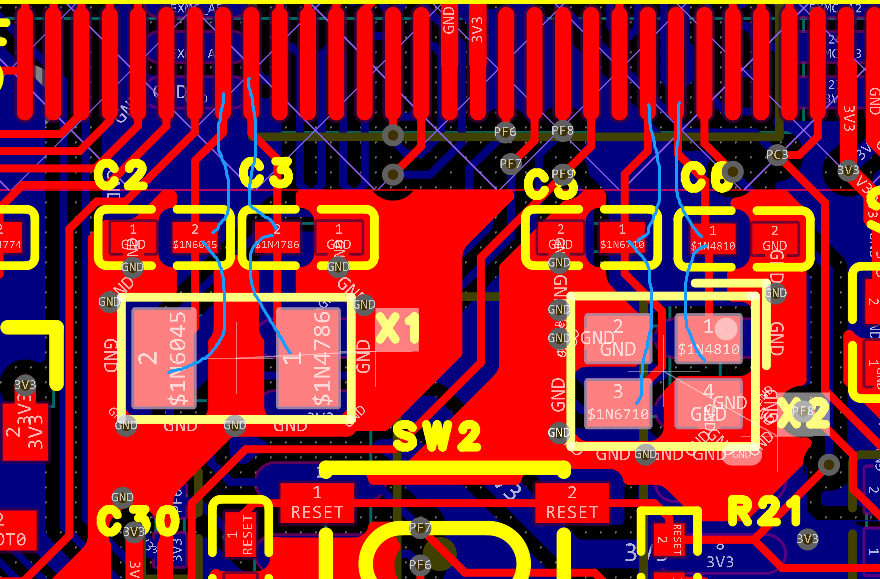

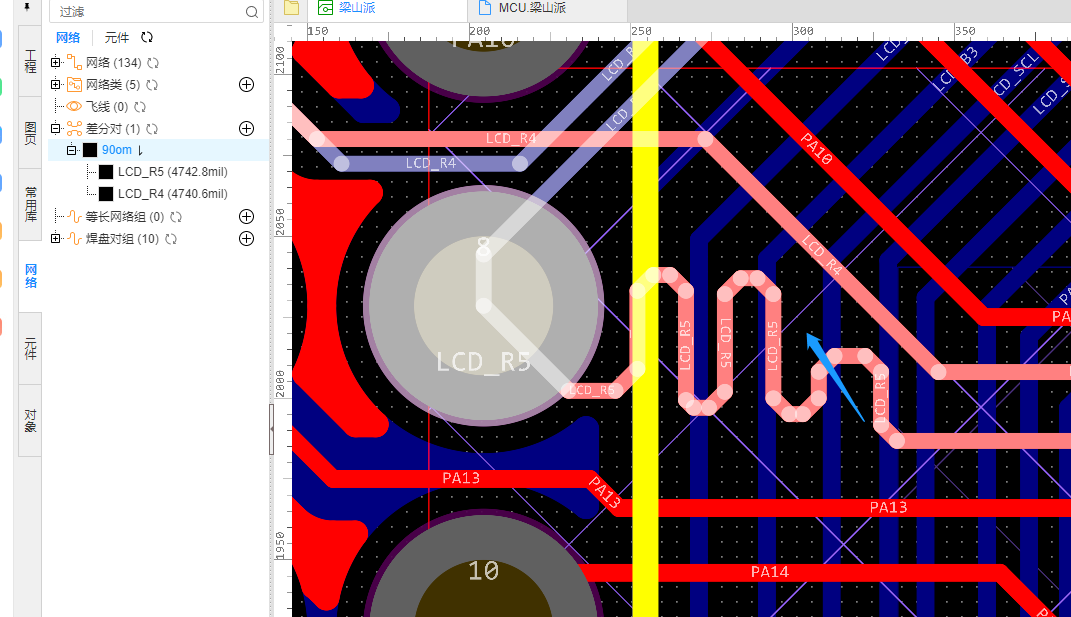

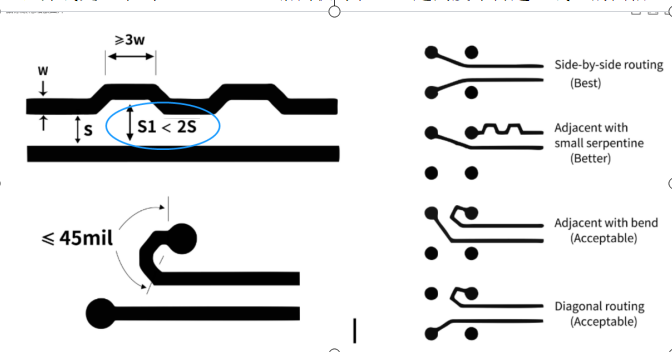

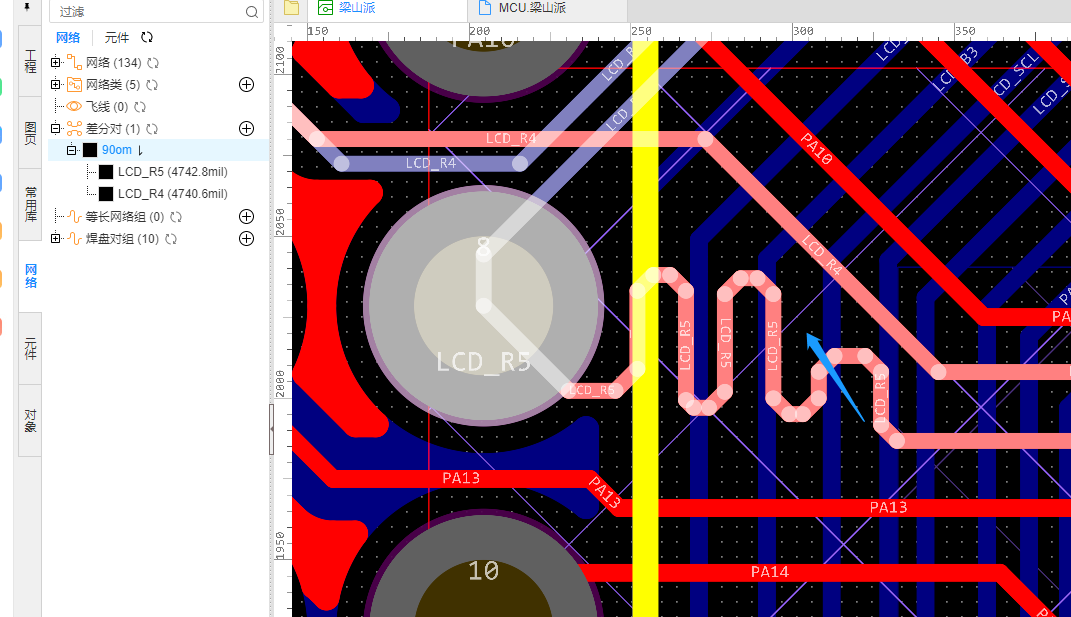

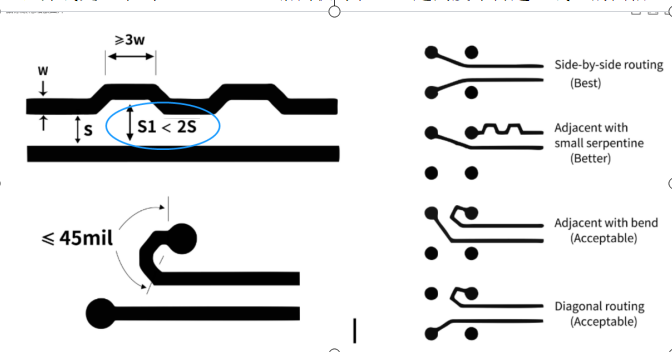

4.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍

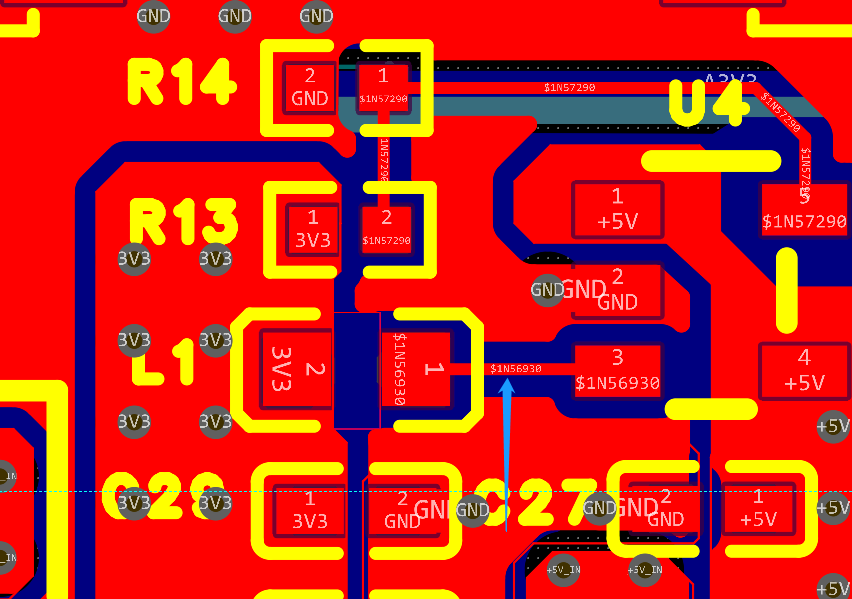

5.时钟包地的地线上需要间隔150mil-200mil打上一个过孔

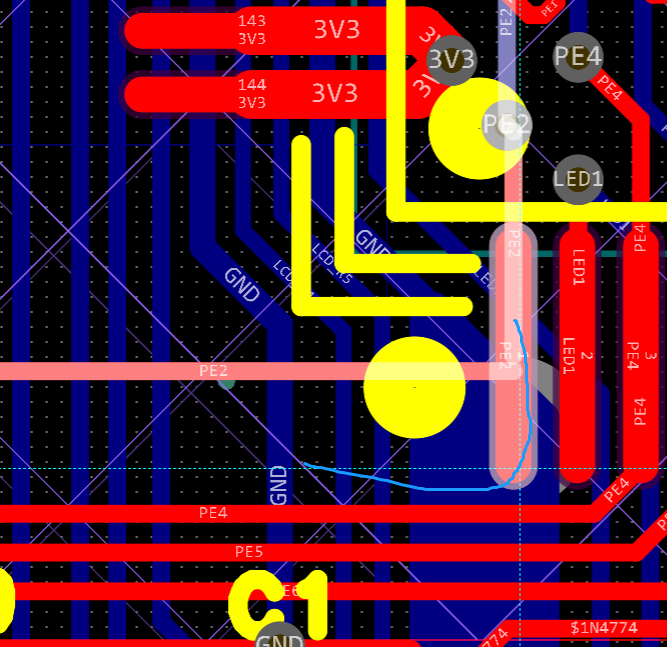

6.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊

晶振下面尽量不要走线

2.晶振需要走类差分形式

3.电源的输入输出需要铺铜处理,铺铜宽度需要满足电源电流大小

4.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍

5.时钟包地的地线上需要间隔150mil-200mil打上一个过孔

6.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊