- 全部

- 默认排序

LDO的前世今生

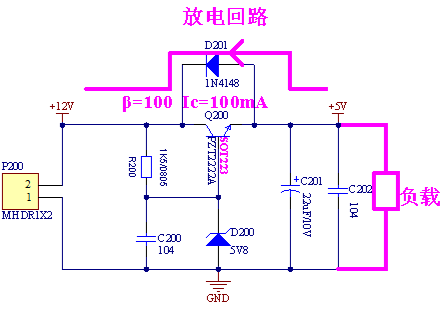

LDO的前世今生 众所周知,开关电源的效率很高,但是输出电压有纹波,噪声很大,不能直接接入单片机控制电路中,而一般选择的方案都是在开关电源的输出端接一级LDO低压差线性稳压电源,可以保证输出到单片机中的电压很稳定,而且在进行AD采样时减

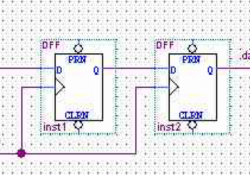

同步时序电路和异步时序电路是数字电路的重要内容,也是小白学习数字电路时重点学习的电路设计课程之一,但如果我们遇见异步时钟域数据同步问题,我们该怎么办?处理跨时钟域问题的核心在于要保证下级时钟对上级数据采样的setup时间或hold时间满足要

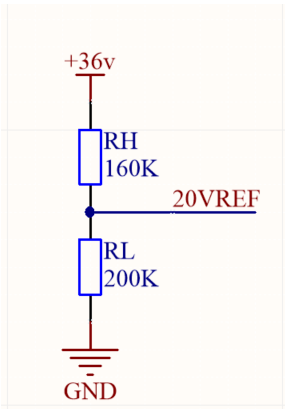

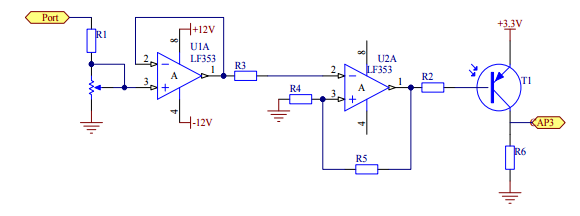

电压采集采样电路设计

电压的采集是我们进行电路设计常常用到的,具体的采集类型上又分为直流采集和交流采集,将源电压通过一系列的电路设计,最终通过AD(数模转换芯片或单片机内部AD)读入MCU,并执行相应的决策,是我们大多设计的要求。下文将通过具体的实例介绍如何设计

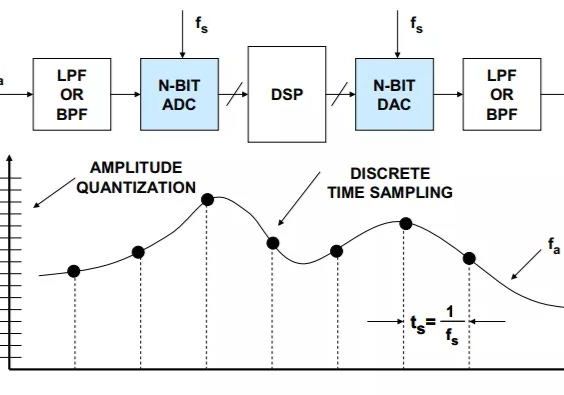

模数转换器即A/D转换器,简称ADC,将采样是利用模拟开关将连续变化的模拟量变成离散的数字量,由于经采样后形成的数字量宽度较窄,经过保持电路可将窄脉冲展宽,形成梯形波。量化是将阶梯形模拟信号中各个电压值转化为某个最小单位的整数倍,便于用数字

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

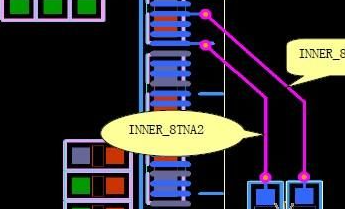

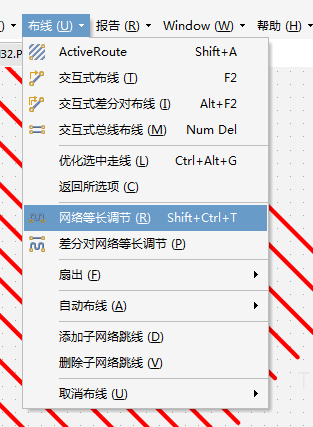

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

利用CS5463芯片可调整温度漂移误差个提高测量精度-CS5463的内部结构框图如图1所示,它由2个可编程增益放大器、2个△-∑调制器、配套的高速滤波器、功率计算引擎、偏置和增益校正、功率监测、串行接口及相应功能寄存器等组成。2个可编程放大器采集电压和电流数据,△-∑调制器对模拟量采样处理,高速数字低通或可选的高通滤波器滤取可用电压电流数字信号,功率计算引擎计算各类型的功率,电压、电流,并将计算的功率值通过串行接口对外输出,既可以接EEPROM,也可以接微控制器。该电路还有能量脉冲信号输出模块,

1.开关电源概述 开关电源的基本构成如下图所示,其中DC-DC变换器用于进行功率转换,他是开关电源的核心部分,此外还有启动、过流和过压保护、噪声滤波等电路。输出采样电路(R1、R2)检测输出电压的变化,并与基准电压Ur比较,误差电压经过放大及脉宽调制电路(PWM),在经过驱动电路控制功率器件的占空比,从而达到调整输出电压大小的目的。 2.开关电源设计要点 1) 第一时间下载主芯片的datasheet,按照推荐的布局布线来进行操作(以TPS55540为例)

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

全站最新内容推荐

- 1AD-全能20期-SMT32-两层板-20期-杨文越

- 290天全能特训班22期-莱布尼兹的手稿 第十九次作业 SDRAM

- 3飞龙套餐Altium Designer篇(PCB、硬件、EMC、单片机)

- 4飞龙套餐PADS篇(PCB、硬件、EMC、单片机)

- 5飞龙套餐allegro篇(PCB、硬件、EMC、单片机)

- 6AD-全能21期-DM642开发板第一次作业

- 72024年中国及31省市3D打印市场分析及国家政策汇总

- 8AD- 杨皓文 第七次作业 2片SDRAM设计(菊花链)

- 990天全能特训班22期AD-沸点-2SDRAM

- 102.4GHz/6GHz Wi-Fi 带通滤波器: ACPF-7A24-TR1、ACPF-W065-TR1 产品介绍、特征及应用

扫码关注

扫码关注