- 全部

- 默认排序

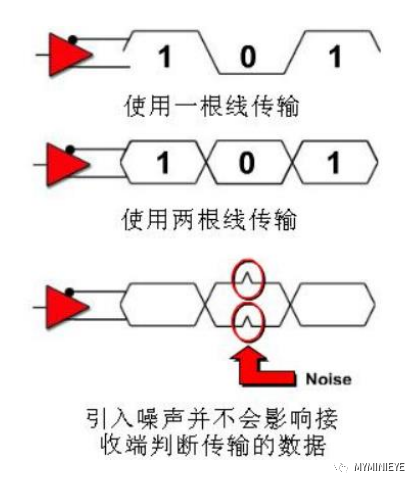

1、差分信号简介1.1 差分信号区别于传统的一根信号线一根地线的做法,差分传输在两根线上都传输信号,这两个信号的振幅相同,相位相反,在这两根线上的传输的信号就是差分信号。信号接收端通过比较这两个电压的差值来判断发送端发送的逻辑状态。在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线

高速PCB设计指南之六

高速PCB设计指南之六第一篇 混合信号电路板的设计准则 模拟电路的工作依赖连续变化的电流和电压。数字电路的工作依赖在接收端根据预先定义的电压电平或门限对高电平或低电平的检测,它相当于判断逻辑状态的“真”或“假”。在数字电路的高电平和低电平之间,存在“灰色”区域,在此区域数字电路有时表现出模拟

步入21世纪后,控制器(MCU)开始呈现出各种类型及功能作用,在此过程中,通信是关键环节,然而不同电平信号的控制器该如何通信?下面来看看如何实现!首先,先了解下电平信号的概念,电平信号是指电子电路中用来表示逻辑状态的电压信号,电压的高低代表

步入21世纪后,控制器(MCU)开始呈现出各种类型及功能作用,在此过程中,通信是关键环节,然而不同电平信号的控制器该如何通信?下面来看看如何实现!首先,先了解下电平信号的概念,电平信号是指电子电路中用来表示逻辑状态的电压信号,电压的高低代表

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

全站最新内容推荐

- 1LED驱动模块RSC6218A 5W-18W迷你高效驱动电源应用-REASUNOS(瑞森半导体)

- 2从零开始成为电子大佬,第一步先识读电源!

- 3IEEE 1588 四通道/八通道系统同步器:8A34001E-000AJG、8A34002E-000NLG、8A34003E-000NBG(器件)

- 4光电器件故障了,如何排除维护?

- 5走进电子元器件,了解热继电器

- 6搞电子设计的人,转行能干什么?

- 7Solder Mask和Paste Mask有哪些不同?

- 8PCB板制造技术水平的标志如何看?

- 9雷军招人:为中国汽车工业全面崛起做贡献!

- 10单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

扫码关注

扫码关注