- 全部

- 默认排序

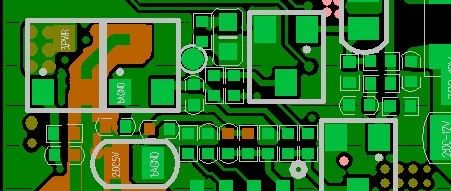

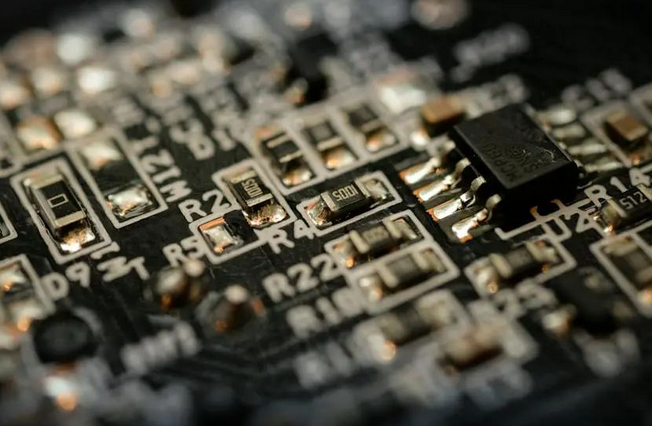

在PCB布局布线时,很多工程师都在发愁去耦电容如何摆放,因为去耦电容直接影响到电路的稳定性和性能,正确摆放去耦电容可有效减少电源噪声,提高系统的抗干扰能力,下面我们来看看应该如何摆放?1、近负载摆放去耦电容应该尽量靠近负载元件,例如芯片、集

高速PCB设计指南之八

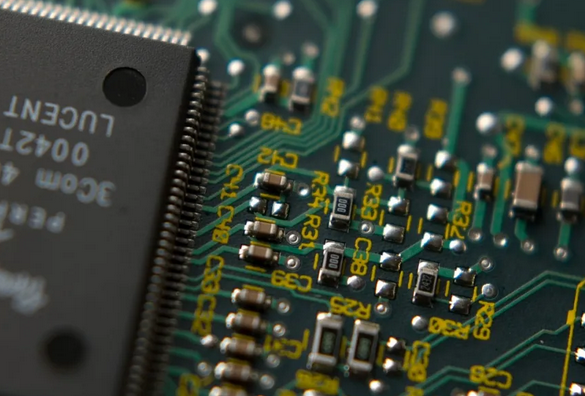

高速PCB设计指南之八第一篇掌握IC封装的特性以达到最佳EMI抑制性能将去耦电容直接放在IC封装内可以有效控制EMI并提高信号的完整性,本文从IC内部封装入手,分析EMI的来源、IC封装在EMI控制中的作用,进而提出11个有效控制EMI的设计规则,包括封装选择、引脚结构考虑、输出驱动器以及去耦电容的

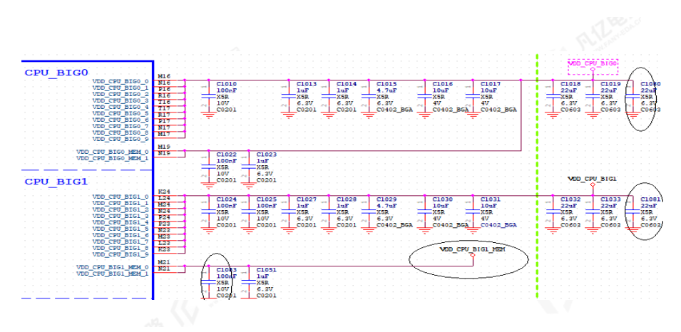

RK3588 VDD_CPU_BIG0/1 电源PCB设计1、如图1所示的滤波电容,原理图上靠近 RK3588的VDD_CPU_BIG电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容GND PAD尽量靠近芯片中心的GND管脚放置,

在电子电路设计中,电容是不可或缺的元件之一,然而了解过电子设计的人,都会发现电路上经常摆放着两个电容,即一个0.1uF电容和一个0.01uF电容,这是为什么?1、0.1uF电容的作用①去耦在电路中,0.1uF电容是以去耦电容存在的,主要用于

电源往往是我们在电路设计过程中最容易忽略的环节。其实,作为一款优秀的设计,电源设计应当是很重要的,它很大程度影响了整个系统的性能和成本。 这里,只介绍一下电路板电源设计中的电容使用情况。这往往又是电源设计中最容易被忽略的地方。很多人搞ARM,搞DSP,搞FPGA,乍一看似乎搞的很高深,但未必有能力为

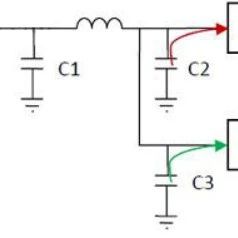

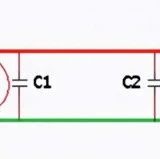

一、旁路和去耦旁路电容(Bypass Capacitor)和去耦电容(Decoupling Capacitor)这两个概念在电路中是常见的,但是真正理解起来并不容易。要理解这两个词汇,还得回到英文语境中去。Bypass在英语中有抄小路的意思,在电路中也是这个意思,如下图所示。couple在英语中是一

关于滤波电容、去耦电容、旁路电容作用及其原理从电路来说,总是存在驱动的源和被驱动的负载。如果负载电容比较大,驱动电路要把电容充电、放电,才能完成信号的跳变,在上升沿比较陡峭的时候,电流比较大,这样驱动的电流就会吸收很大的电源电流,由于电路中的电感,电阻(特别是芯片管脚上的电感,会产生反弹),这种电流

了解直流电源的人都知道,其负载变化会引起电源噪声,举个例子,如:当数字电路从一个状态转换为另一种状态时,将在电源线上产生一个很大的尖峰电流,形成瞬变噪声电压,因此需要配置去耦电容来抑制负载噪声,提高系统的可靠性,那么该如何做?1、去耦电容的

在电子设备中,电源的稳定性和可靠性非常重要,能够保证整个电子系统的正常运行,其中电源分配网络(PDN)的设计尤为关键,去耦电容作为PDN中的重要组成部分,其合理配置对提高PCB可靠性有着不可或缺的作用,本文将探讨如何有效配置去耦电容,希望对

如果观察许多大佬的硬件电路设计,很容易发现他们都会放去耦电容,这样的做法是可以消除电源噪声,保障关键元件如ROM、RAM等的稳定工作,但很多小白不太清楚,所以今天我们来讲讲为什么要这么摆放去耦电容,需要注意什么?一般来说,PCB板上的走线、

扫码关注

扫码关注