- 全部

- 默认排序

想要进行蓝牙开发,第一步肯定要对蓝牙协议有所了解。除了要对蓝牙的一些专业术语有所熟悉,还应该对蓝牙协议每层功能有一定认知。概略图:物理层(PHY):调制、解调方式,工作频段(2402-2480MHZ),通信速率等控制。链路层(LL):负责广

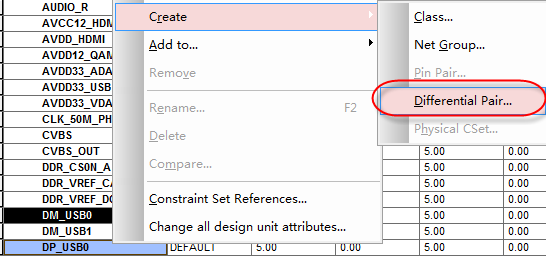

答:设计PCB过程中,若设计中有差分对信号,则需要将是差分的2个信号设置为差分对,设置差分对有2种方式:手动添加及自动添加。

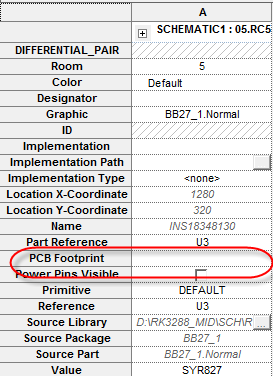

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36002): Property "PCB Footprint" missing from instance U3: HI3716MDMO3B_VER_A, ETH PHY_12 (3.95, 1.35).解决的办法如下所示:第一步,错误描述是封装PCB Footprint的缺失,缺失的器件是U3,含义就是U3这个器件在绘制原理图时没有做封装的匹配,这一栏是空的;第二步,在原理图中找到U3这个器件,

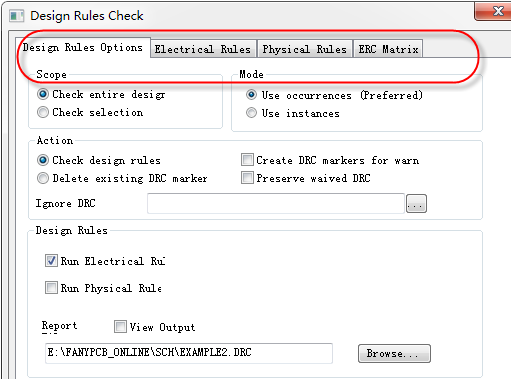

答:第一步,选择原理图的根目录,然后执行菜单Tools-Design Rules Check,进行设计规则的检查,如图3-61所示; 图3-61 进行DRC检查示意图第二步,弹出的DRC检测界面中,有4项的参数可以设置,可以依次进行选择,如图3-62所示,Design Rules Options为检查的参数设置,Electrical Rules为电气规则检查参数设置,PHYsical Rules为物理规则检查参数设置,ERC Matrix为DRC矩阵设置是否报DRC。 图3-

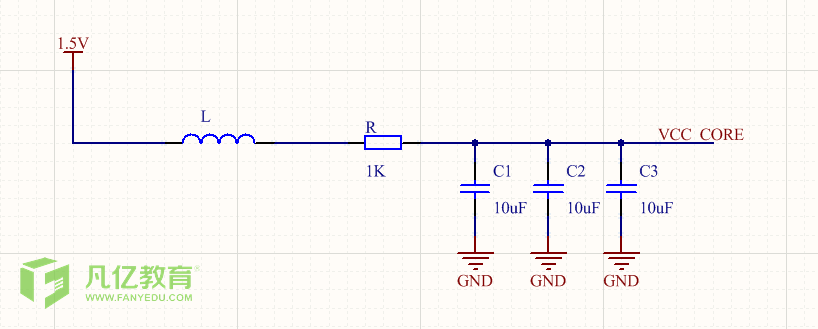

假设下图是一个单板上的PHY芯片的核心电源滤波电路设计。 * 根据这个PHY芯片的资料,这个电源对噪声等方面的干扰特别明显,所以这个设计中不仅采用了,LC滤波电路。还在电感L的后面串联了一个1欧的电阻R。LC滤波电容能滤除高频段噪声。而在这个电路中的这个电阻R不但能衰减高频段噪声,而且能衰减低频段噪声。可以作为一个全频段的衰减器,这种电路设计方法一般用于对噪声特别敏感的电源,如时钟的电源等等。但是单板的长时间运行发现,电阻R经常爆裂。 * 电路设计中选用的电阻R,尺寸是040

全站最新内容推荐

- 1常规变压器耦合型自激调频式开关电源电路分析讲解

- 2低压MOS在多电平逆变器上的应用-REASUNOS瑞森半导体

- 3走进电子元件,了解双稳态触发器

- 4模拟电路太难读?有没有可能是你不会看!

- 5要使用电烙铁,应该注意什么?

- 6硬件设计:4.10 通过这个实验,你会深刻认识到电感滤波与电容滤波电路的区别(为什么电容型滤波电路不能用在大电流环境)

- 7硬件设计:4.8-4.9 电感教程_滤波电路_低通滤波电路为什么分为电容型和电感型

- 8硬件设计:4.7电感教程_为什么有些开关电源在上电时会过压_怎么解决

- 9硬件设计:4.6 电感教程_5V电压升至1万V电压的工作原理

- 10硬件设计:4.5 电感教程之开关电源教程(boost型)_重新认识电感的重要性

扫码关注

扫码关注