- 全部

- 默认排序

allegro报错?

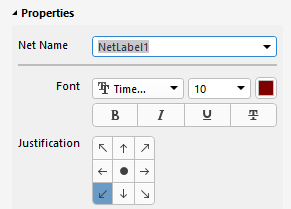

请教个问题WARNING(ORCAP-1589): Net has two or more aliases - possiBLE short?这个警告可以不管吗

在绘制原理图时对于一些较长的连接网络或者数量比较多的网络连接,绘制时如果全部采用导线的连接方式去连接,不方便设计。这个时候可以采取网络标号(Net LaBLE)方式来协助设计,网络标签和线都是连接网络的方式。

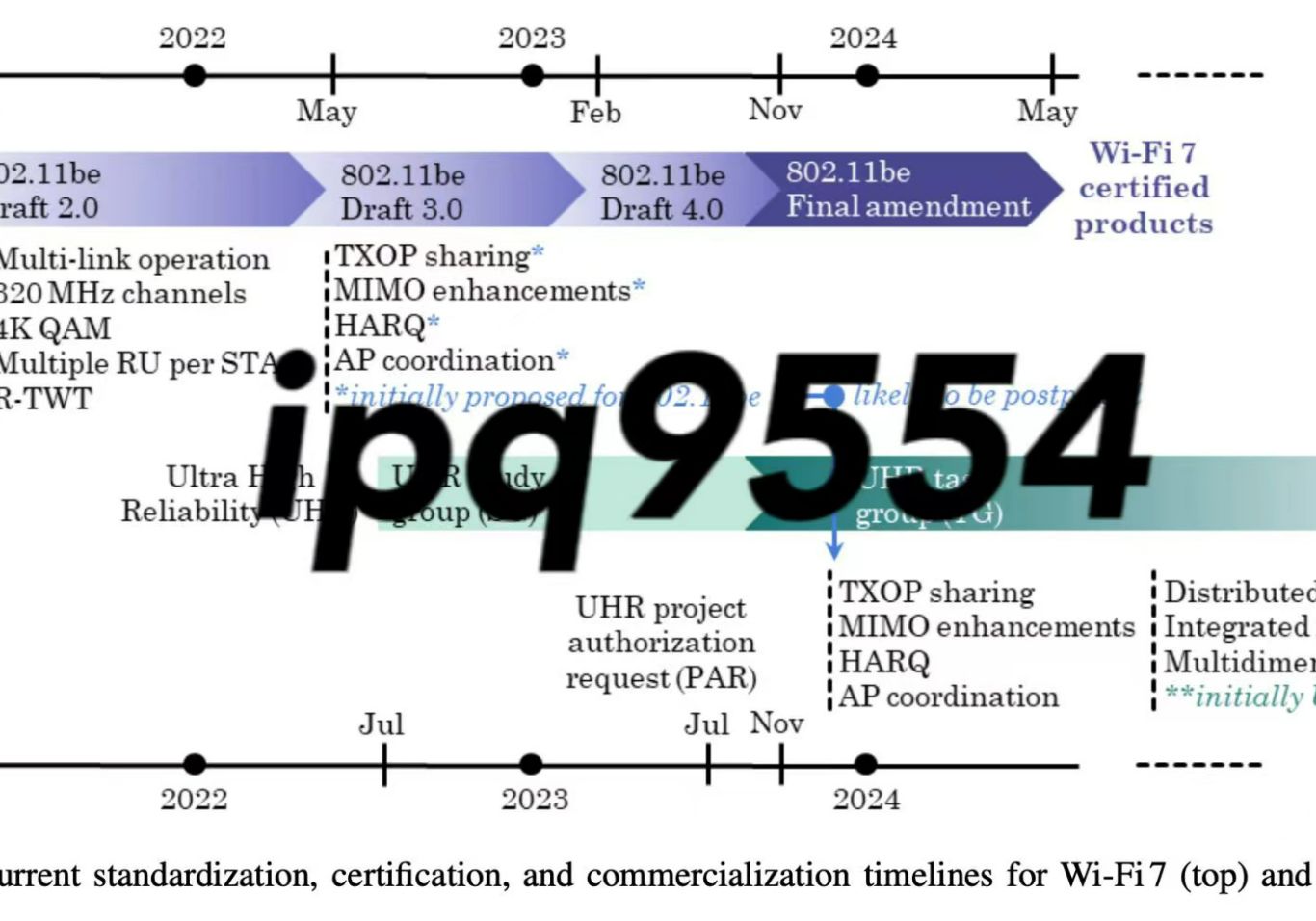

As the demand for faster and more reliaBLE wireless internet continues to grow, companies are constantly looking for way

PADS添加地符号

在连线状态下单击鼠标右键点击“接地”(或者组合快捷键ctrl+space),可以添加地符号,如图4-41,4-42所示。切换地符号和切换电源符号的操作一样,按住(ctrl+taBLE)快捷键即可切换。图4-41 选择接地命令图4-42 添加

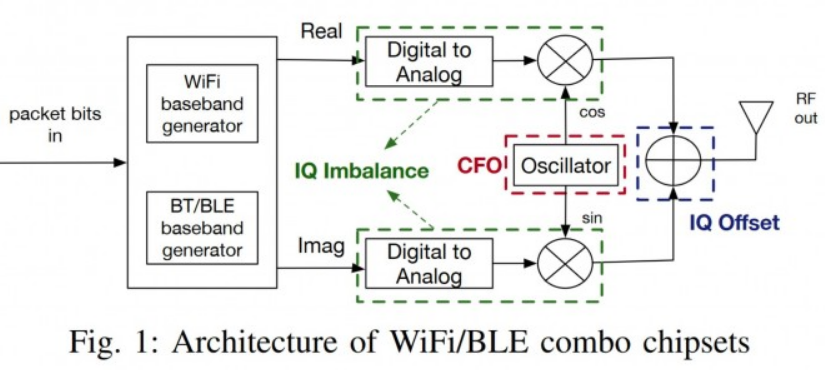

近年来,随着科技迭代更新,蓝牙设备连接和蓝牙功能已成为智能手机的标配功能之一,我们只需通过打开蓝牙就能连接蓝牙设备,如AirPods、蓝牙耳机等,但你知道吗,可能有不法分子正通过蓝牙跟踪我们。即使没有蓝牙设备连接,你的智能手机也将持续发出低

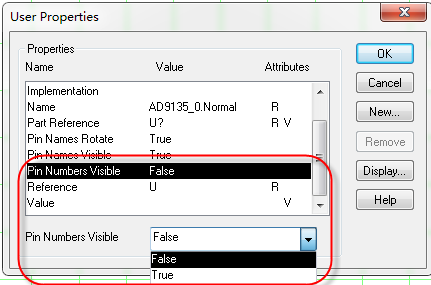

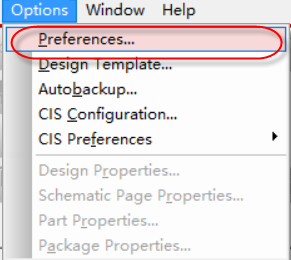

答:在设计的时候,有一些原理图符号不需要将管脚编号显示,比如电阻、电容、二极管等元器件,我们的操作方法如下:第一步,打开所要隐藏管脚编号的库文件,点击菜单Options→Part Properties编辑属性;第二步,在弹出的属性框中选中Pin Numbers VisBLE,修改Value值属性即可;第三步,需要显示管脚编号的,Value值那一栏选择True;隐藏管脚编号的,Value值那一栏选择False,如图2-48所示: 图2-48 隐藏与显示管脚编号示意图

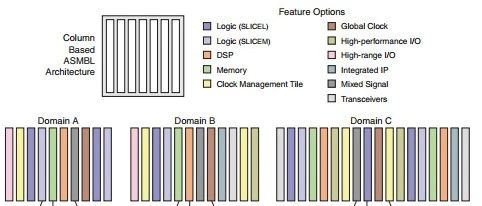

CLB是指可编程逻辑功能块(ConfiguraBLE Logic Blocks),顾名思义就是可编程的数字逻辑电路。CLB是FPGA内的三个基本逻辑单元。CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都可配置,在Xilinx公司的FPGA器件中,CLB由2个 相

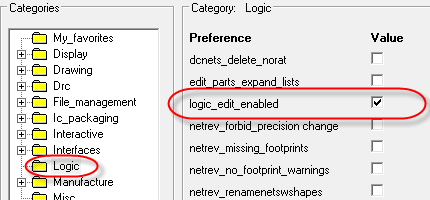

答:在第375问中我们讲解了如何手动去添加元器件,这样直接添加的元器件本身是没有网络的,这一问呢,我们讲述一下如何手动的在PCB中去修改网络与添加网络,具体操作的步骤如下所示:首先,要勾选允许元器件编辑与网络的选项,才可以进行进行编辑,进入用户参数设置,选择logic,将logic edit enaBLEd选项勾选上,如图6-135所示;

5G市场漫谈

作为一家致力于为当前及未来5G射频设备打造经济高效测试解决方案的供应商,泰瑞达正携手集成设备制造商(IDM)、无晶圆半导体设计商(faBLEss)和半导体封测外包商(OSAT),共同搭建5G发展新生态。文︱编辑部图︱网络5G,一项被描述为“与印刷机、电报、蒸汽机、电力、互联网同等重要的通用技术”,其

答:在运用orcad绘制原理图之前,首先要把整个的格点设置好,设置的方法如下:第一步,执行菜单Options→Preference…,在弹出的界面中选择Grid Display选择,在此选项中对格点进行设置,如图3-8所示; 图3-8 格点设置示意图第二步,左侧的Schematic Page Grid是原理图设计的格点,右侧Part and Symbol Grid是封装库设计的格点;Ø VisiBLE选项中,勾选Displayed是在设计时

扫码关注

扫码关注