半导体封装简介

半导体封装是现代电子系统的核心环节,负责将芯片集成到功能系统中,同时保护其免受环境和机械应力的影响。封装的核心任务是将半导体器件(如CPU、GPU、存储器)连接到基板上,实现芯片与印刷电路板(PCB)之间的电气信号传输。传统封装以单芯片集成为主,但Chiplet(小芯片)与异构集成的兴起彻底改变了这一领域[1]。

Chiplet是一种模块化半导体设计方法,将复杂系统拆分为多个可独立优化的功能块(如逻辑单元、I/O模块、存储器)。与传统的单片系统级芯片(SoC)不同,Chiplet允许采用不同制程节点和材料制造各模块。异构集成则通过先进基板将这些异构的Chiplet封装为单一系统,从而提升性能、降低成本并缩短上市时间。例如,AMD的Instinct MI250X计算加速器通过硅桥和扇出型再分布层(RDL)集成GPU与高带宽内存(HBM)。

基板技术的演进

为满足小型化、高互联密度和热管理的需求,基板技术经历了显著变革。

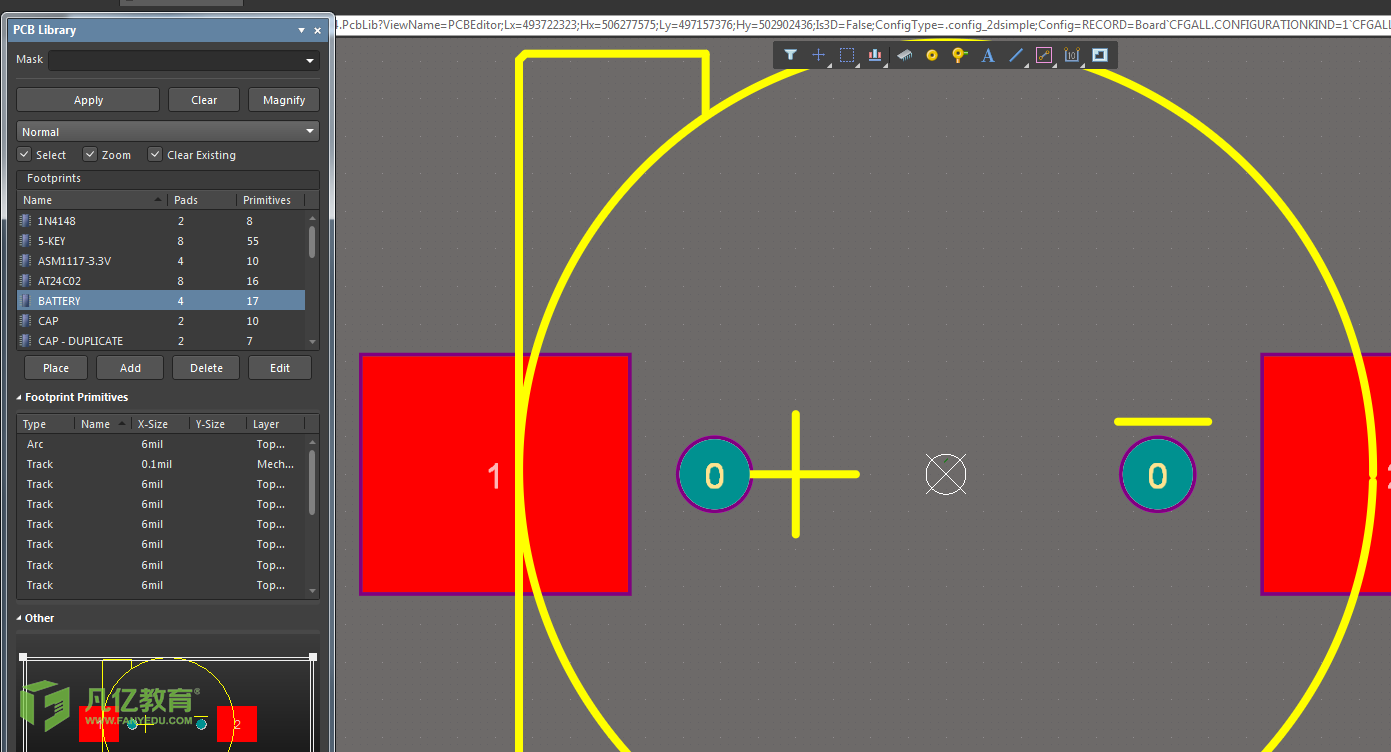

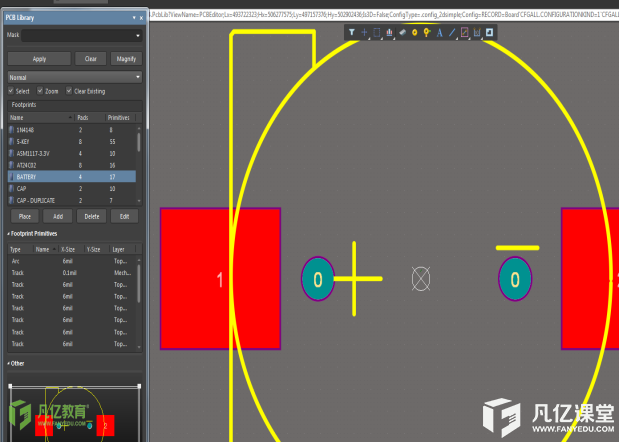

早期基板:积层结构与扇出型RDL,多芯片模块(MCM)的早期基板采用有机核心上的积层结构IBM的表面层压电路(SLC)技术(图1)是这一领域的先驱,通过堆叠介电层和导电层实现高密度互连。积层基板因成本与性能的平衡至今仍广泛应用。

图1: IBM的SLC技术,剖面图展示积层基板结构,包含微孔和用于连接PCB的焊球。

扇出型晶圆级封装(FOWLP)是一项突破性技术。与传统基板不同,FOWLP通过再分布层(RDL)在重构晶圆上重新布局连接,省去焊球和底部填充材料。英飞凌的早期研究(图2)展示了扇出型RDL如何实现更薄、更经济的封装,同时提升散热性能。苹果iPhone的A10处理器即采用FOWLP技术,以紧凑尺寸实现高性能。

图2: 扇出型RDL基板与积层基板对比,英飞凌的扇出型RDL技术(右)省去了焊球与倒装焊步骤,相比传统积层基板(左)更简化。

2.5D与3D集成:TSV中介层与混合键合,随着晶体管密度接近物理极限,2.5D集成应运而生。该技术利用硅通孔(TSV)中介层(图3)实现Chiplet的水平与垂直互连。TSV支持逻辑、存储器和I/O芯片间的高带宽通信,例如NVIDIA的H100 GPU通过TSV中介层连接逻辑芯片与HBM堆栈。

图3: TSV中介层与有机中介层对比,(a) 含硅通孔的TSV中介层;(b) 含嵌入式硅桥的有机中介层。

在3D堆叠中,混合键合(图4)以铜-铜直接键合取代焊球,降低延迟与功耗。英特尔的Foveros技术将计算单元堆叠在主动中介层上,而台积电的CoWoS-L通过硅桥实现超高密度互连。

图4: 混合键合桥接技术,无凸点铜-铜键合相比传统焊球实现更精细的互连间距与更简化的基板结构。

先进基板的重要性

先进基板解决了性能、能效与可扩展性的关键瓶颈。

硅桥与有机桥接,英特尔嵌入式多芯片互连桥(EMIB)(图5)在有机基板中嵌入高密度互连,省去TSV中介层。EMIB在成本与带宽间取得平衡,例如英特尔Agilex FPGA通过微凸点连接FPGA与HBM。

图5: 英特尔EMIB结构,EMIB桥接(高亮部分)实现Chiplet间的局部高密度互连。

玻璃核心基板,英特尔的玻璃核心基板(图6)凭借超平整度、尺寸稳定性与10倍互联密度,成为AI与数据中心应用的理想选择。然而,玻璃与PCB的热膨胀系数(CTE)差异与初期高成本仍是挑战。

图6: 玻璃核心基板优势,核心优势包括机械稳定性、耐高温性及与光电子技术的兼容性。

光电共封装(CPO),光电共封装(图7)将光电子集成芯片(PIC)与电子芯片(EIC)集成于同一基板,以光纤替代铜互连。思科的3D异构集成方案在玻璃中介层中嵌入激光器与波导,实现低功耗太比特级数据传输。

图7: PIC与EIC的3D异构集成方案,多种配置展示光电子与电子组件的集成方式,包括TSV中介层与混合键合。

传统封装的当前挑战

尽管技术进步,传统基板仍面临以下限制:

热应力与机械应力,材料间的热膨胀系数(CTE)差异导致焊点失效。例如,有机基板(CTE约24 ppm/°C)比硅(2.8 ppm/°C)膨胀更剧烈,造成微凸点应力(图8)。玻璃基板(4.8 ppm/°C)虽缓解芯片级应力,但因刚性在PCB界面产生新问题。

图8: C4焊点可靠性对比:玻璃与有机核心,热应变对比凸显芯片与PCB级可靠性的权衡。

良率与成本问题,TSV中介层与混合键合等技术初期良率较低。玻璃基板虽前景广阔,但需构建全新制造生态,初期成本与良率问题显著。

设计复杂度,集成多厂商Chiplet需统一接口标准(如UCIe)。异构系统还需先进散热方案,例如AMD的3.5D Instinct MI300采用液冷应对堆叠芯片的热管理。

总结

先进基板技术是延续摩尔定律、满足AI与高性能计算需求的关键。从TSV中介层到玻璃核心,这些技术解决了带宽、功耗与散热难题。然而,克服成本、良率与标准化障碍仍需产业链协作。英特尔玻璃基板与台积电CoWoS-L路线图表明,未来封装技术将依赖材料创新与系统级协同设计。

扫码关注

扫码关注