MCU时钟往往外接晶振、电容,有的会并一个1M电阻,PCB布局时怎么布局好?MCU出来是先晶振后电容好还是先电容后晶振好?还有1M的电阻放那个位置比较好?布线应该注意什么?

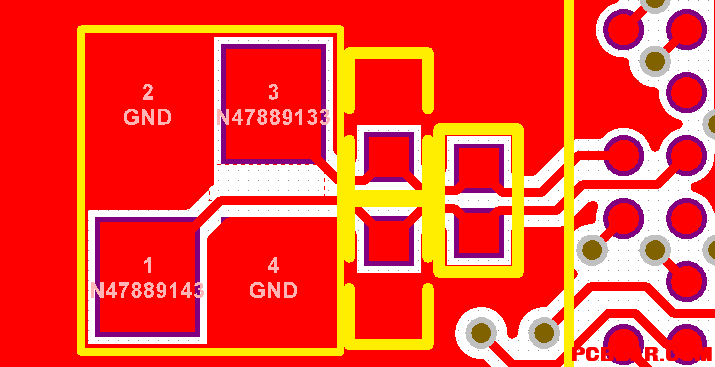

晶振是一个干扰源,本体表层及第二层禁止其他网络走线,并注意在晶体引脚及负载电容处多打地过孔。

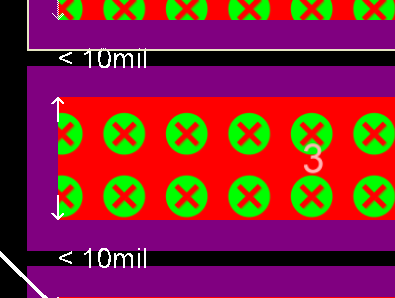

晶振走线尽量短,晶振走线尽量不要打孔换层,走在和器件同面,并且采用“π”型滤波方式,如图所示。

0

回答于 · 2019-07-31 17:55

猜你想问

人工解答

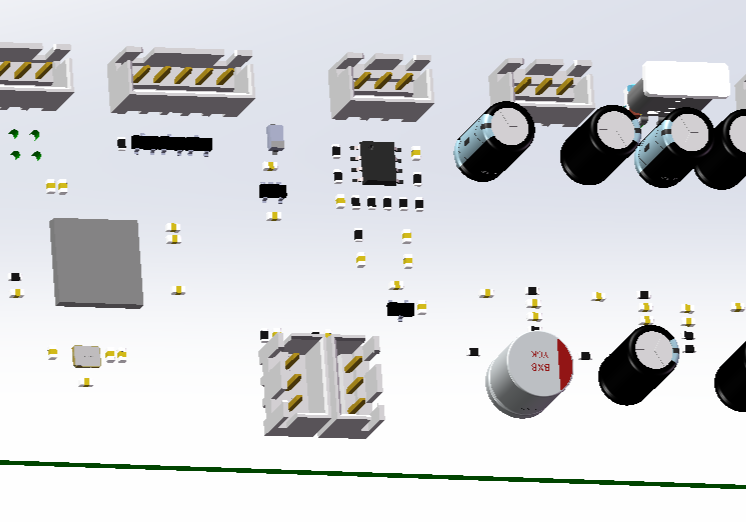

AD23导出STEP格式PCB模型,PCB板本体是透明的如何解决?

2024-03-19 14:47:07

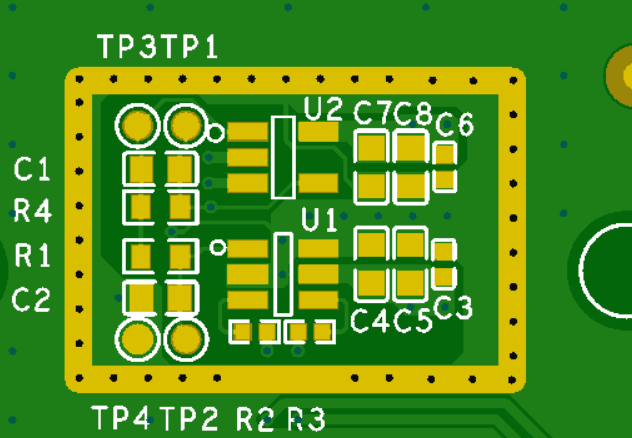

想问一下各位大神,为什么我画一个焊盘当做m2螺丝孔,元件的封装没问题,加到板子上下面就有一个正方体,这正常么

2023-12-27 11:02:45

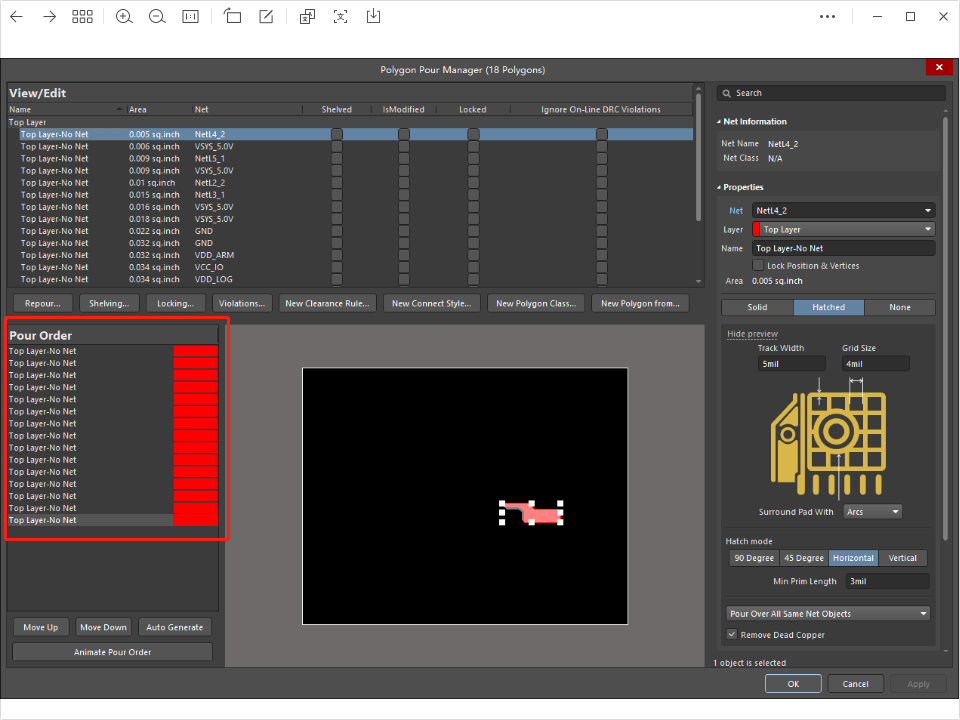

Altium Designer如何调整铜皮的铺铜优先级?

2023-11-27 18:53:51

为什么gerber传到嘉立创没有地过孔了

2023-11-27 18:54:46

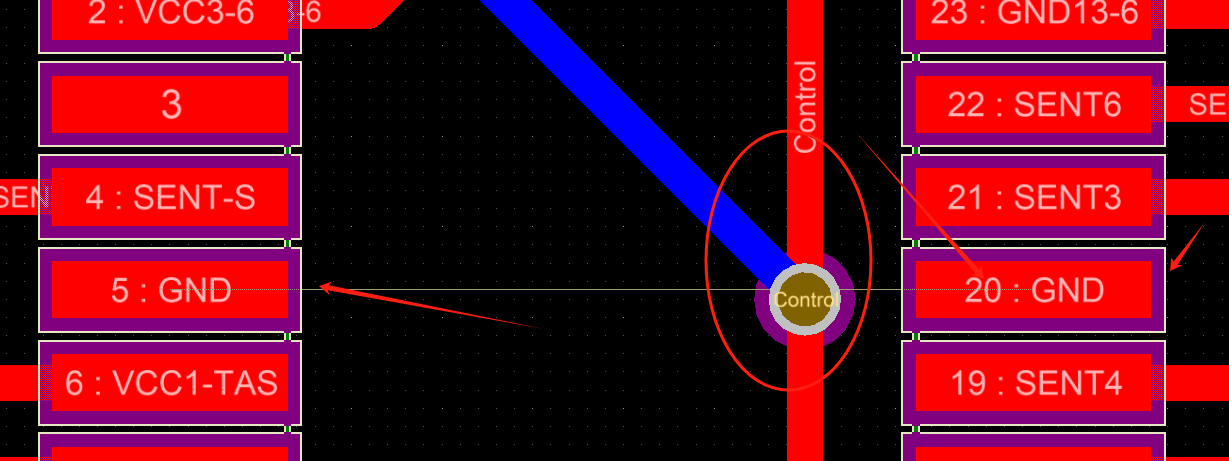

两个GND顶层和底层都铺铜了 为啥还是连不上啊?

2023-11-27 18:49:32

Altium PCB焊盘和焊盘之间报错小于10mil提示,如何解决

2023-11-27 18:51:10

热门直播

更多>>

扫码关注

扫码关注