- 全部

- 默认排序

电路设计防静电原理解析

一、静电放电波形和能量频谱 静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前辈电路设计了很多静电放电模型。 常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。芯片级一般用HBM做测试,而电子产品则用IEC 6 1000-4-2的放电模型做测试。为对 ESD 的测试进行统一规

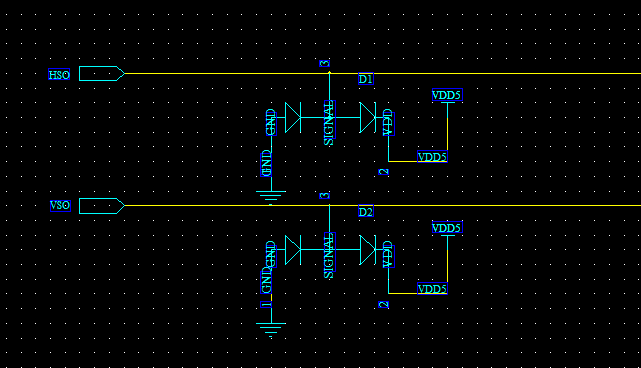

PCB设计中,对于静电的防护,一般采用隔离、增强单板静电免疫力和采用保护电路三项措施来进行电路设计。 深圳pcb设计培训班对于PCB上的静电敏感元器件,在布局时要考虑其布局在远离干扰的地方,特别是离静电放电源越远越好,还有就是电气隔离,金属外壳; 增强免疫能力,在面积允许的情况下,可以在PCB板周围设计接地防护环,可以参考CompactPCI规范。大面积地层、电源层,对于信号层,一定要紧靠电源或者地层,保证信号回路最短,对于干扰源高频电路等,可以局部屏蔽或者单板整体屏蔽,在电源、地脚附近加不

一块好的电路板,除了实现电路原理功能之外,还要考虑EMI、EMC、ESD(静电释放)、信号完整性等电气特性,也要考虑机械结构、大功耗芯片的散热问题,在此基础上再考虑电路板的美观问题,就像进行艺术雕刻一样,对其每一个细节进行斟酌。

纵观成功的电子产品,基本都要具备五个特点:一 性能稳定; 二 整体美观; 三 便于应用; 四 成本合理 ; 五 方便量产; 偏重哪一点,都不能称之为成功的产品。这五点都与pcb布局有关,换句话说,好的,合理的布局是要充分考虑以上五点的,,所以说布局是产品成功与否非常重要的一环。高速PCB设计中,布局更是重要,其合理性直接关系到后续的布线,信号传输的质量,EMI, EMC,ESD等问题,

ESD、EMI、EMC设计是电子工程师在电子设计中遇到常见难点,电磁兼容性(EMC)就是指机器设备或系统软件在其电磁自然环境中符合规定运作并不对其自然环境中的一切机器设备造成难以忍受的电磁干扰的工作能力。因而,EMC包含2个层面的规定:一方面就是指机器设备在一切正常运作全过程中对所属自然环境造成的电磁干扰不可以超出一定的限制值;另一方面就是指器材对所属自然环境中存有的电磁干扰具备一定水平的抗扰度,即电磁敏感度。说白了电磁干扰就是指一切

开关电源ESD测试教程

1. 开关电源的几种保护OCP, OLP, OVP, OTP, ESD,UVLO分别是什么意逐周期电流限制保护(OCP),限制最大输出电流;过载保护(OLP),限制最大输出功率;VDD过压保护(OVP),限制最高输入电压;温度保护(OTP),限制工作时的最高温升;ESD静电保护,即静电释放,避免由于静电引起芯片或者电子元件损坏;以及低压关闭(UVLO),欠压锁定,限制最低入输入电压。过压保护开关和过载保护开关有什么区别?1、负载如果是阻性负载,当电源有故障,负载上的电压有可能大幅上升,而电流的上

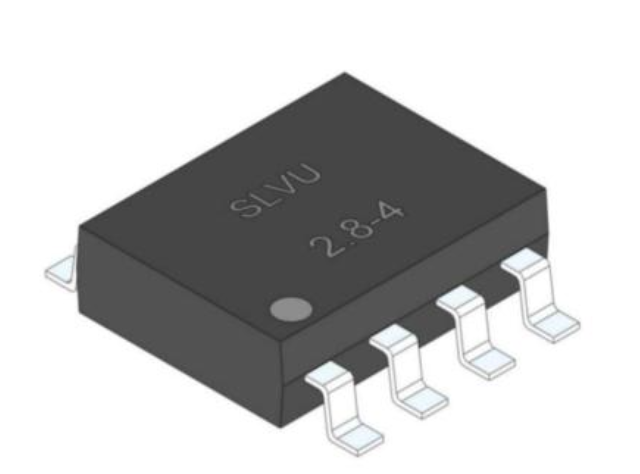

Littelfuse全新50A单向瞬态抑制二极管阵列系列适用于消费类电子产品-SP1250分散式单向瞬态抑制二极管采用专有的硅雪崩技术制造。该二极管阵列可为消费电子设备提供高ESD(静电放电)保护。

ADM2582E/ADM2587E是具备±15 kV ESD保护功能的完全集成式隔离数据收发器,适合用于多点传输线路上的高速通信应用。其内部集成的RS-485驱动器带有一个高电平有效使能电路。

某接地台式产品,对接地端子处进行测试电压为6KV的ESD接触放电测试时,系统出现复位现象。测试中尝试将接地端子与内部数字工作地相连的 Y电容断开,测试结果并未明显改善。

扫码关注

扫码关注