1、走线长度应包含过孔和封装焊盘的长度。

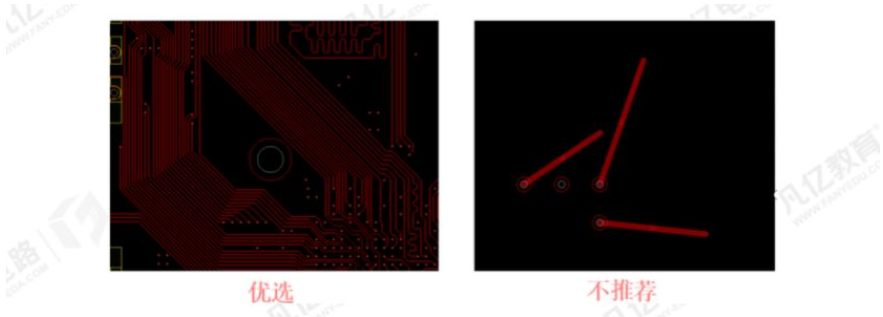

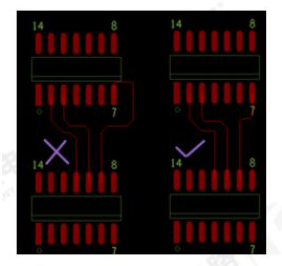

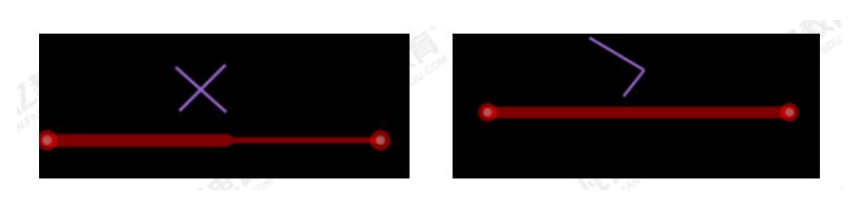

2、布线角度优选135°角出线方式,任意角度出线会导致制版出现工艺问题。

图1 PCB布线的角度

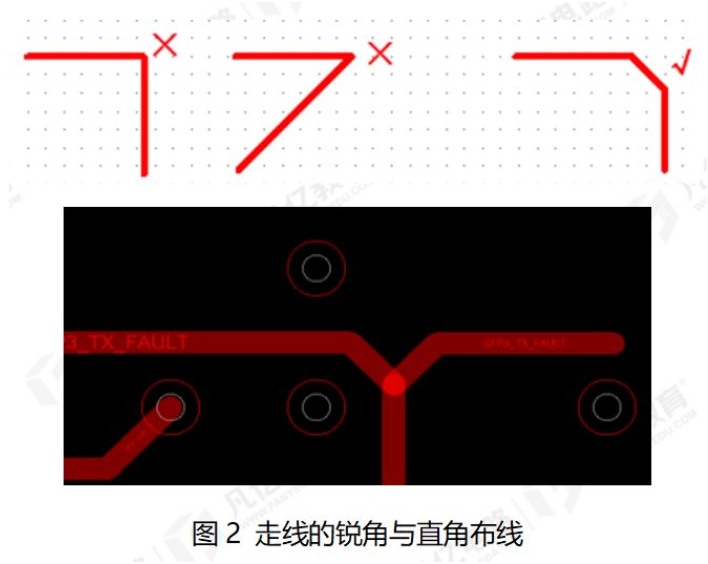

3、布线避免直角或者锐角布线,导致转角位置线宽变化,阻抗变化,造成信号反射,如图2所示。

图2 走线的锐角与直角布线

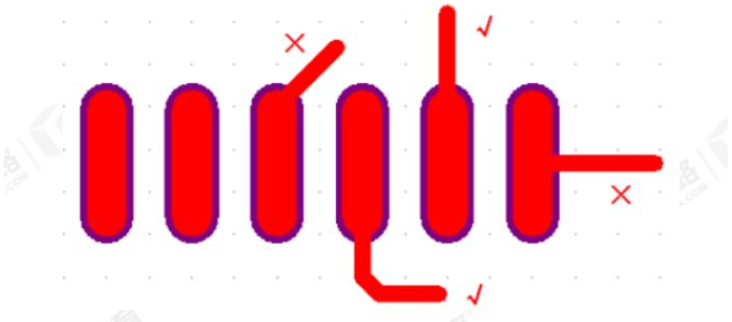

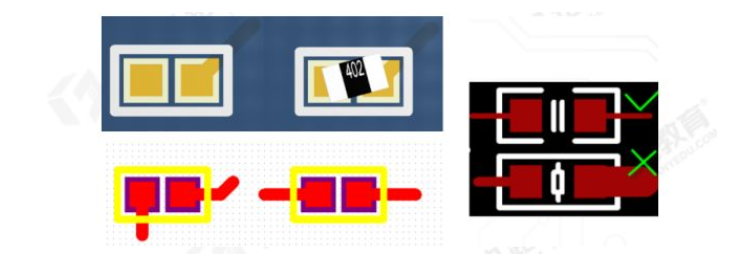

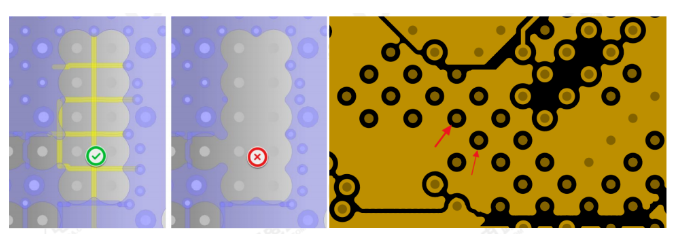

4、布线应从焊盘的长方向出线,避免从宽方向或者焊盘四角出线,布线的拐角离焊盘位置6mil以上为宜,如图3所示

图3 PCB沿焊盘长边出线

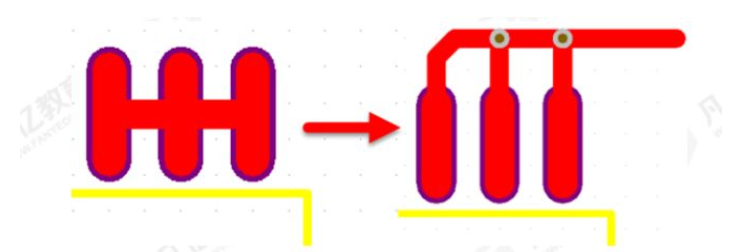

5、如图4所示,相邻焊盘是同网络的,不能直接相连,需要先连接出焊盘之后再进行连接,直接连接容易在手工焊接时连锡。

图4 相同网络焊盘走线链接方式

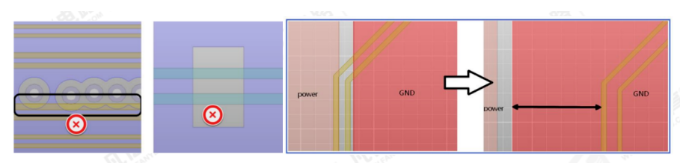

6、对于小CHIP器件,要注意布线的对称性,保持2端布线线宽一致,如一个管脚铺铜,另一管脚也尽量铺铜处理,减少元件贴片后器件漂移旋转,如图5所示。

图5 CHIP类焊盘的正确出线

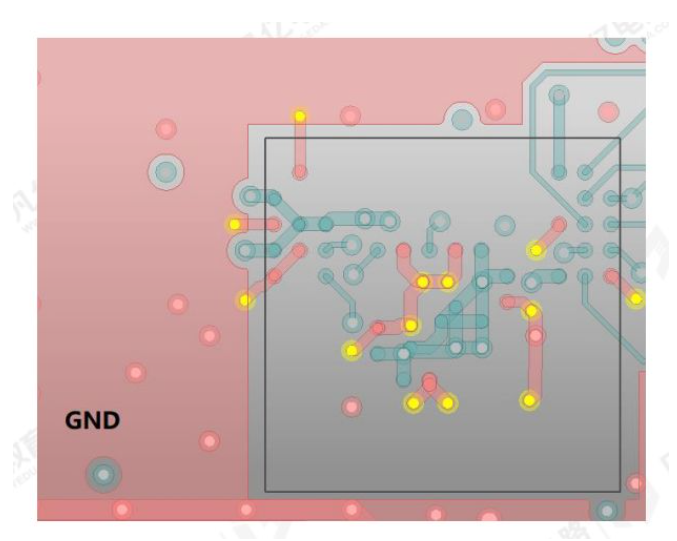

7、对于有包地要求的信号,须保证包地的完整性,尽量保证在包地线上进行打GND孔处理,2个GND孔间距不能过远,尽量保持在50-150mil左右,如图6所示。

图6 PCB的包地走线

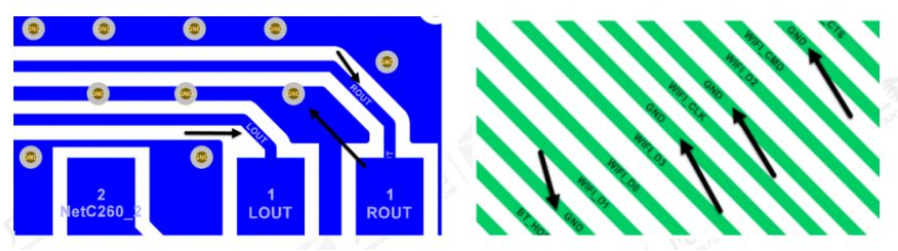

8、走线应有完整且连续的参考层平面,避免高速信号跨区,建议高速信号距离参考平面的边沿至少有 40mil,如图7所示。

图7 走线的夸分割

9、由于表贴器件焊盘会导致阻抗降低,为减小阻抗突变的影响,建议在表贴焊盘的正下方按焊盘大小挖去一层参考层。常用的表贴器件有:电容、ESD、共模抑制电感、连接器等等,如图8所示。

10、如图9所示,信号线与其回路构成的环路面积要尽可能小。环路面积小,对外辐射小,接收外界的干扰也小。

图8 标贴器件焊盘的挖空处理

图9 布线的环路面积的缩小

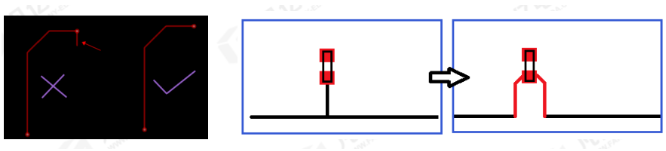

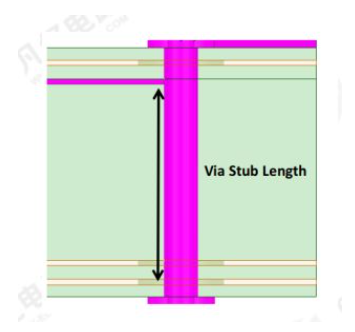

11、如图10,布线不允许出现STUB,布线尽量减小残桩长度,建议残桩长度为零。并且避免过孔残桩效应,尤其是残桩长度超过 12mil 时,建议通过仿真来评估过孔残桩对信号完整性的影响,如图11所示。

图10 Stub走线及布线残桩

图11 过孔的残桩

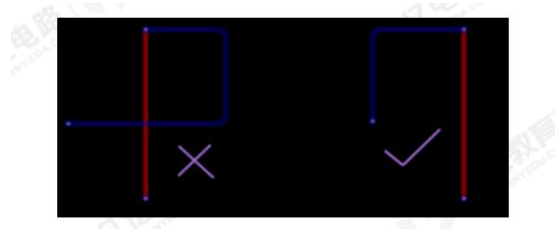

12、尽量避免走线在不同层形成自环。在多层板设计中容易出现此类问题,自环将引起辐射干扰。如图12所示。

图12 PCB布线的自环

13、建议不要在高速信号上放置测试点。

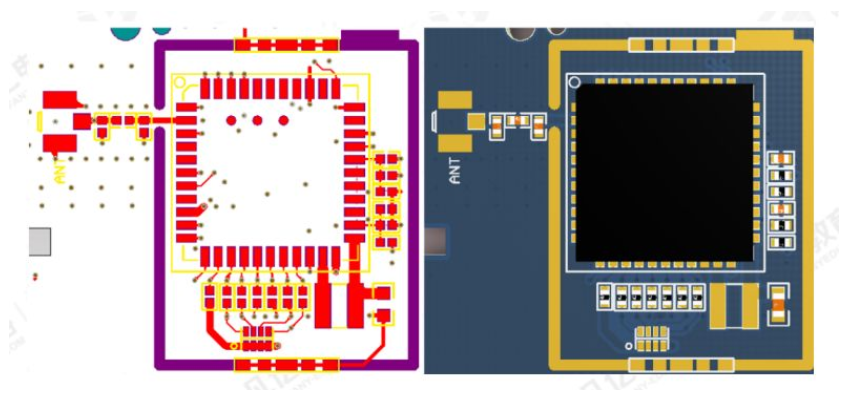

14、对于会产生干扰或者敏感的信号(如射频信号),须规划屏蔽罩,屏蔽罩宽度常规为40mil(一般保持30mil以上,可与客户生产厂家确认),屏蔽罩上尽量多打GND过孔,增加其焊接效果。如图13所示。

图13 敏感模块的屏蔽罩处理

15、同一网络的布线宽度应保持一致,线宽的变化会造成线路特性阻抗的不均匀,当传输的速度较高时会产生反射。在某些条件下,如接插件引出线,BGA封装的引出线类似的结构时,因间距过小可能无法避免线宽的变化,应该尽量减少中间不一致部分的有效长度,如图14所示。

图14 走线线宽的突变

16、IC管脚出线的线宽要小于或者等于焊盘宽度,出线宽度不能比焊盘宽度大,部分信号因载流等要求,线宽较宽的,布线可先保持与管脚宽度一致,布线引出焊盘后6-10mil左右再把线宽加粗处理,如图15所示。

图15 走线不宜超出焊盘宽度

17、布线必须连接到焊盘、过孔中心。

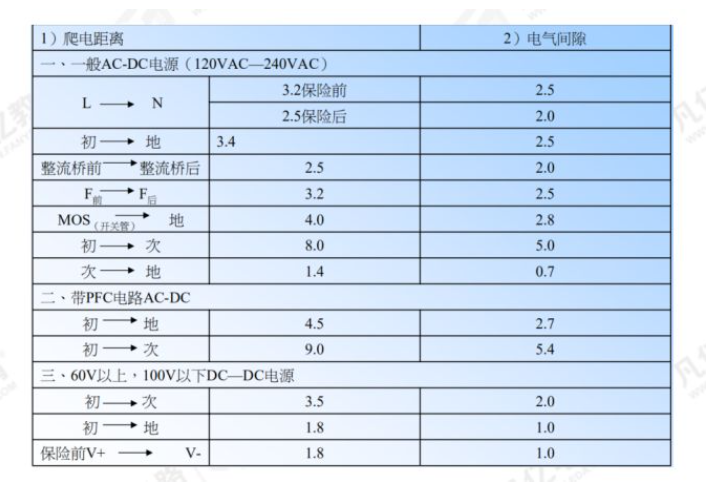

18、有高压信号,须保证其爬电间距,具体参数如16所示。

图16 爬电间距与电气间隙表

19、设计中包含多片DDR或者其他存储器芯片的,须向客户确认布线拓扑结构,确认是否有参考文档。

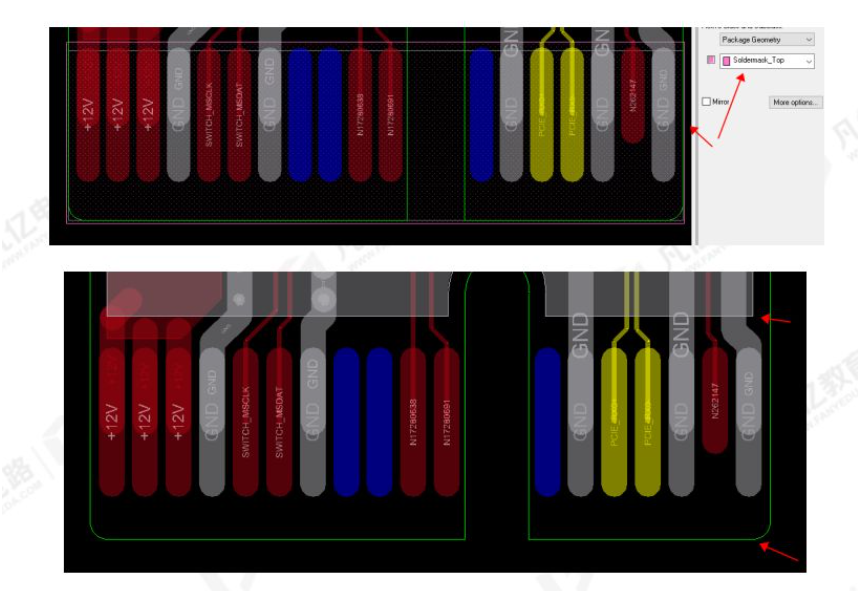

20、金手指区域需要开整窗处理,多层板设计时,金手指下方所有层的铜应作挖空处理,挖空铜皮的距离板框一般3mm以上,如图17所示。

图17 金手指的开窗与挖空

21、布线应提前规划好瓶颈位置的通道情况,合理规划好通道最窄处的布线能力。

图18 PCB布线通道

22、耦合电容尽量靠近连接器放置。

23、串接电阻应靠近发送端器件放置,端接电阻靠近末端放置,如eMMC时钟信号上的串接电阻,推荐放在靠近 CPU 侧(400mil以内)。

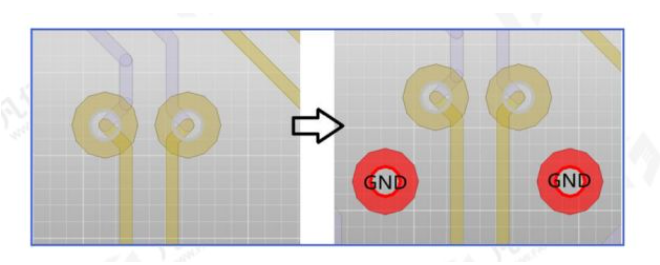

24、建议在IC(如eMMC 颗粒、FLASH颗粒等)的地焊盘各打1个地通孔,有效缩短回流路径, 如图19所示。

图19 GND焊盘的过孔打孔

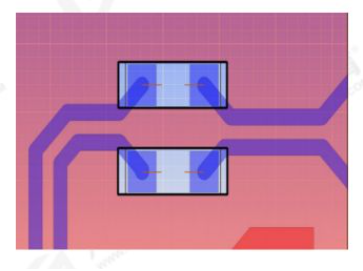

25、建议ESD器件的每个地焊盘都打一个地通孔,且通孔要尽量靠近焊盘,如图20所示。

图20 ESD器件GND焊盘的打孔

26、避免在时钟器件(如晶体、晶振、时钟发生器、时钟分发器)、开关电源、磁类器件、插件过孔等周边布线。

27、走线换层,且换层前后参考层为地平面时,需要在信号过孔旁边放一个伴随过孔,以保证回流路径的连续性。对于差分信号,信号过孔、回流过孔均应对称放置,如图21(a)所示;对于单端信号,建议在信号过孔旁边放置一个回流过孔以降低过孔之间的串扰,如图21(b)所示。

图21(a)差分换层过孔示意图

图21(b)单端信号换层过孔示意图

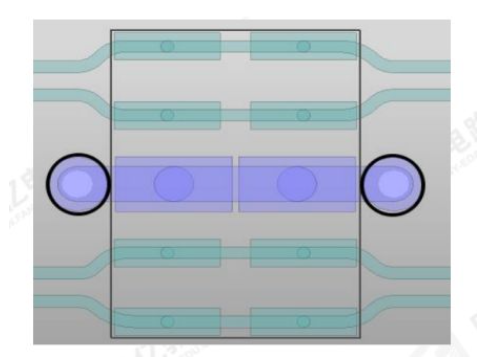

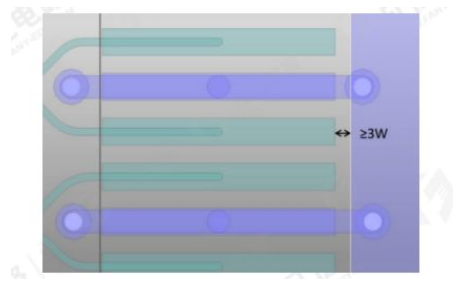

28、连接器的地铜皮距离信号 PAD至少要大等于3倍线宽,如图22所示。

图22 GND铜皮与连接器PAD的间距要求

29、在BGA区域平面断开处用走线连接,或者进行削盘处理,以免破坏平面完整性,如图23所示。

图23 BGA区域平面铜皮的处理

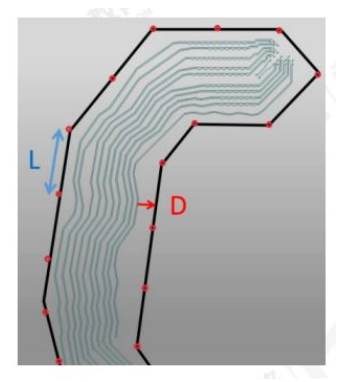

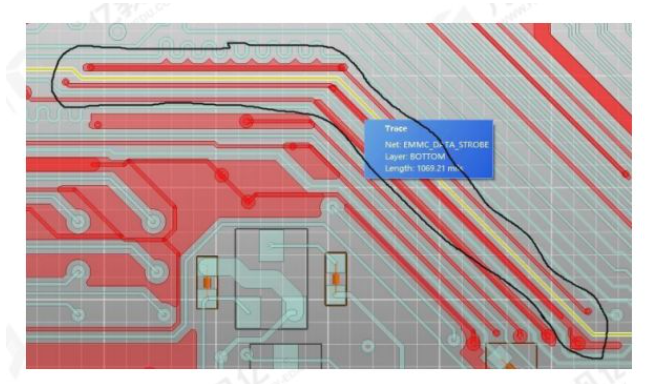

30、PCB布线需要包地处理时,推荐包地方式如下,如图24所示,L 为包地线地过孔间隔; D 为包地线距离信号线之间的间距,建议≥4*W。

31、有些重要的高速单端信号,比如时钟信号、复位信号等(如 emmc_clk、emmc_datastrobe、RGMII_CLK 等等)建议包地。包地线每隔 500mil 至少要打一个地孔,如图25所示。

图24 PCB的包地布线

图25 重要信号线的包地处理

声明:本文凡亿教育原创文章,转载请注明来源!

扫码关注

扫码关注