信号完整性和电源完整性是高速PCB设计的两大重要概念,是电子小白重点学习的重要知识,但针对这两个概念,很多小白依然处于半懂不懂状态,所以下面将带领小伙伴们走进了解信号完整性和蒂娜元完整性。

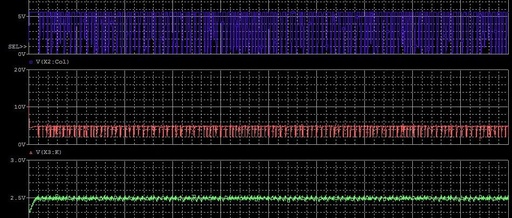

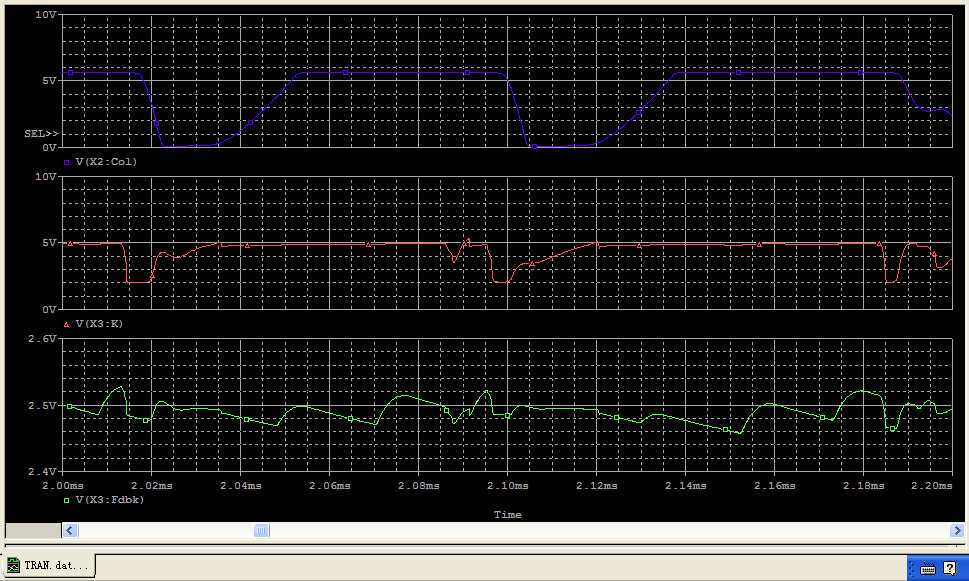

一般来说,信号完整性定义为信号在电路中能以正确时序和电压做出响应的能力,即指在信号线上的信号质量。信号具有良好的信号完整性是指电路中信号达到的电乐电平数值和波形形状信号完整性问题一般不是由某单一因素引起的,而是在板级设计中多种因素共同引起的。信号完整性问题主要表现为几个方面:延迟、反射、串扰、振荡、地弹和电磁兼容性(EMI)。

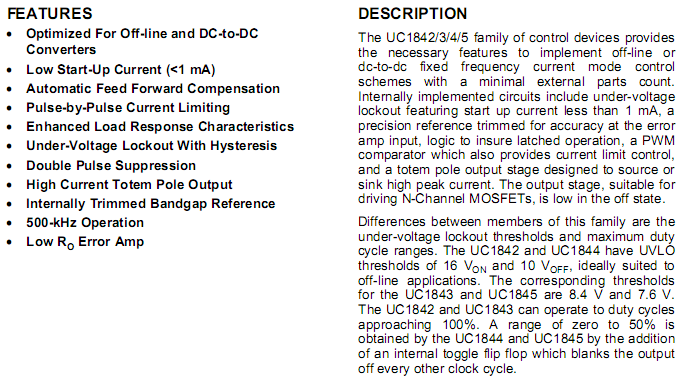

相对于信号完整性,电源完整性是一个较新的研究领域,它被认为是高速高密度PCB设计目前最大的挑战之一。

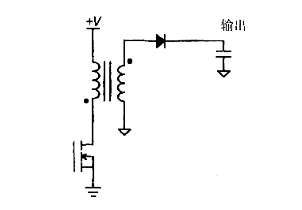

电源完整性是指在高速电子线路中,电源传输系统在不同频率上,由于阻抗特性不同,使PCB板上电源层与地层间的电压在电路板的各处不尽相同,从而造成供电不连续,产生电源噪声,使芯片不能正常工作:同时由于高频辐射,电源完整性问题还会带来EMC/EMI问题,如果不能很好解决电源完整性问题,将严重影响系统的正常工作。

在研究信号完整性和电源完整性时,反射、过冲和下冲,同步切换及地弹是分析中主要研究的对象。

1、反射

反射是在传输线上信号的回波,信号功率(电压和电流)一部分传输到线上并达到负载处,而另一部分被反射回源端,源端与负载端阻抗不匹配将引起线上反射,负载将一部分电压反射回源端,如果负载阻抗小于源阻抗,反射电压为负。反之,如果负载阻抗大于源阻抗,反射电压为正,布线的几何形状、不正确的线端接、经过连接器的传输及电源平面的不连续等因素的变化俊辉导致此类反射。

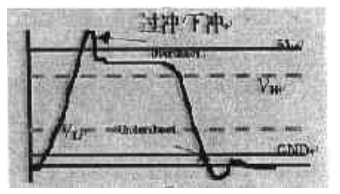

2、过冲与下冲

过冲指信号跳变的第一个峰值或谷值超过规定的电压值,对于上升沿是指最高电压而对于下降沿是指最低电压。下冲是指下一个谷值或峰值,信号过冲和下冲是由集成电路切换速度过高及信号传输路径反射引起的,过分的过冲将引起保护二极管工作,导致电路器件过早失效,过分的下冲将引起假的时钟或数据错误(误操作)。

由于文章篇幅限制,将此文分为上下两篇,欲看下篇可点击右侧连接《走进了解信号完整性和电源完整性(上)》。

扫码关注

扫码关注