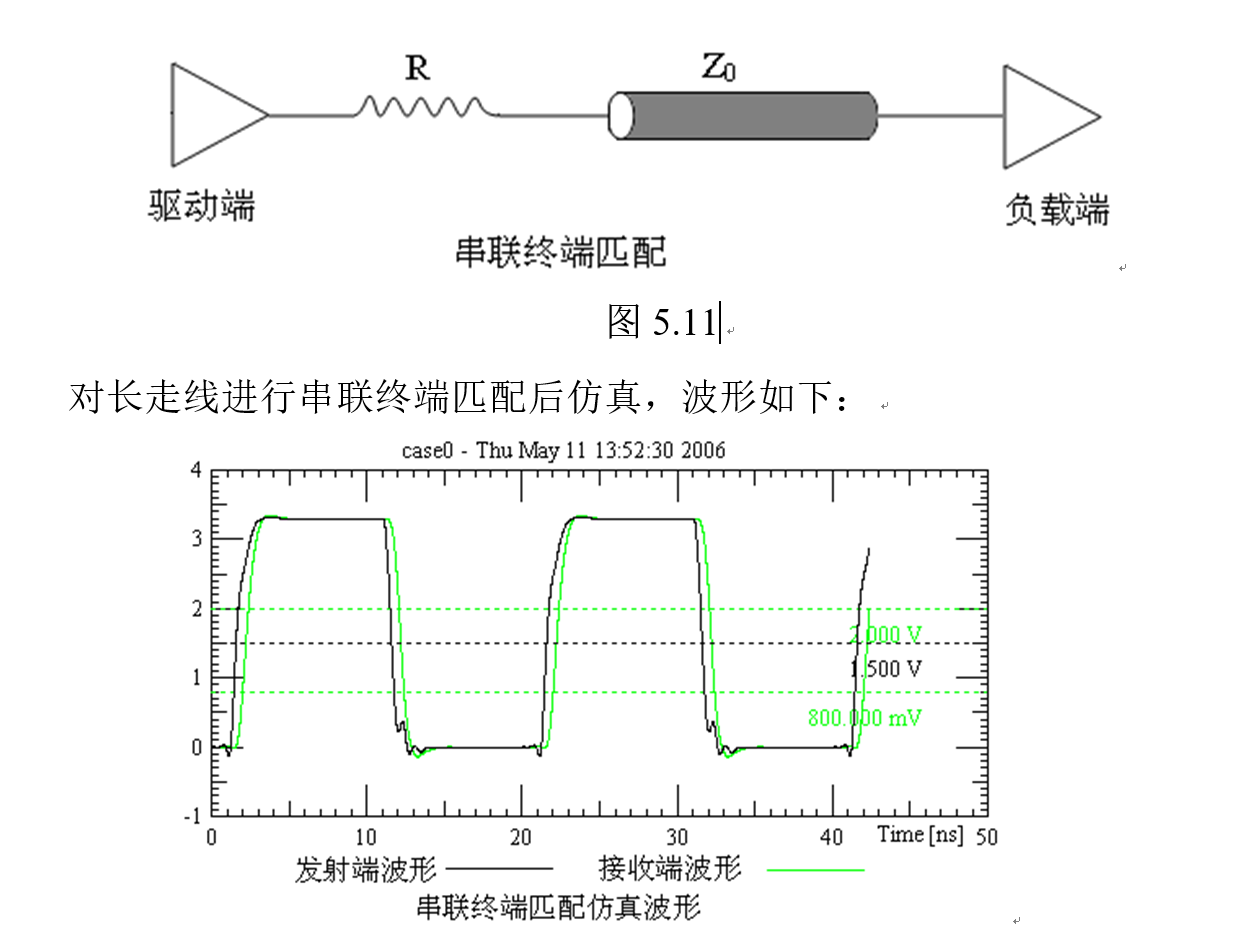

串联终端匹配技术,也称之为后端终端匹配技术,不同于其它类型的终端匹配技术,是源端的终端匹配技术。串联终端匹配技术是在驱动器输出端和信号线之间串联一个电阻。驱动器输出阻抗R0以及电阻R值的和必须同信号线的特征阻抗Z0匹配。对于这种类型的终端匹配技术,由于信号会在传输线、串联匹配电阻以及驱动器的阻抗之间实现信号电压的分配,因而加在信号线上的电压实际只有一半的信号电压。

李增(WareLEO) 关注Ta

李老师,13年+模拟电路和数字电路及程序设计经验,著有多本CADENCE和高速信号仿真书籍,熟悉CADENCE,PADS,AD,MULTISIM,ADS,SIGRITY,ANSYS,EM等EDA和分析工具,通过长期不懈的学习,探索与总结,已初步形成了一套基于高速PCB设计的实践经验及理论,积累上万粉丝。

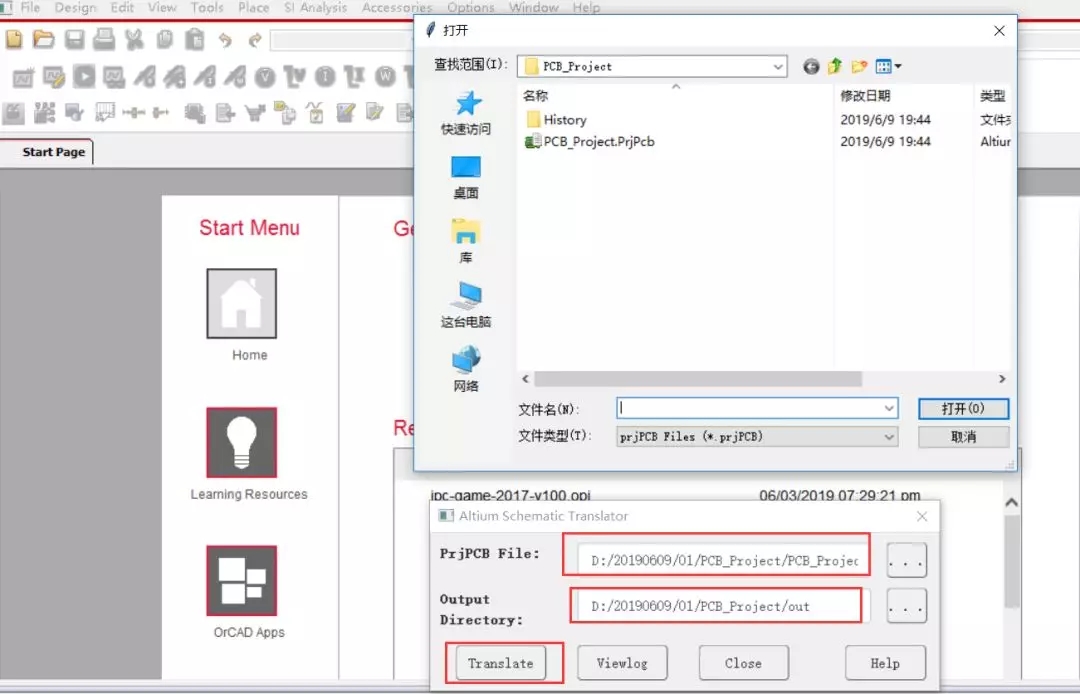

OrCAD Capture作为行业标准的PCB原理图输入方式,是当今世界最流行的原理图输入工具之一,具有简单直观的用户设计界面。不管是用于设计模拟电路、复杂的PCB、FPGA和CPLD、PCB改版的原理图修改还是用于设计层次模块,OrCAD Capture都能为设计师提供快速的设计输入工具。

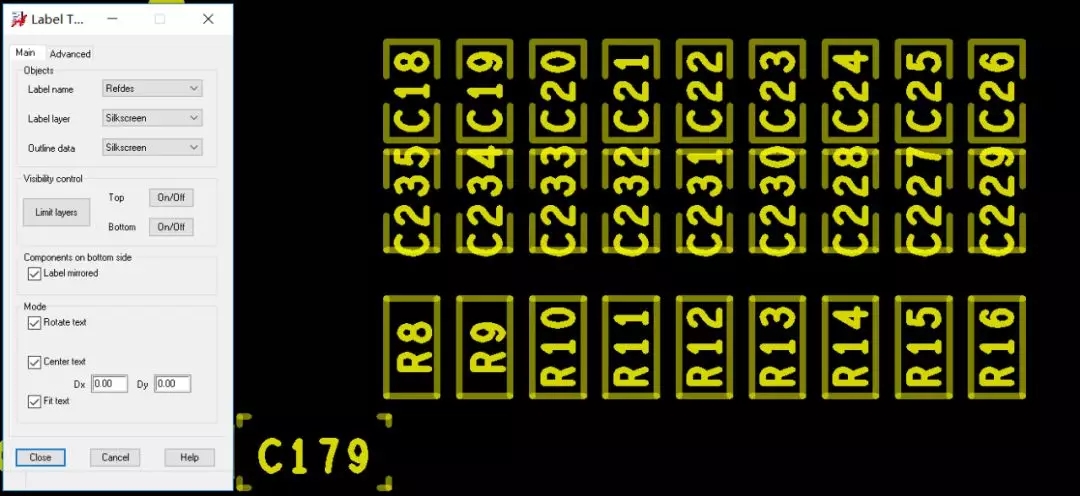

Allegro Productivity Toolbox组件所带来了很多高级命令,今天我们一起学的Label Tune就是其中一个。Label Tune是用来做批量的元件字符对齐操作的命令,可以支持对丝印、显示、装配层的字符对齐操作。我们知道PCB设计里面,丝印可以给贴片和识图的工程师提供一个位置参考,可以让工程师能够快速的找到元件在PCB上的位置。如下图所示,这样整齐的丝印排列可以让工程师快速定位元件位置。

本课程介绍Proteus软件使用讲解。透过次课程Proteus快速入门网络课程,学员能基本了解Proteus的常用功能并能使用Proteus软件进行仿真。

Cadence17.4软件的界面变化后,软件的功能也进行了很大的调整,更加能够适应高速电路和高密度,柔性和刚柔结合设计,背钻异形槽孔的设计等。

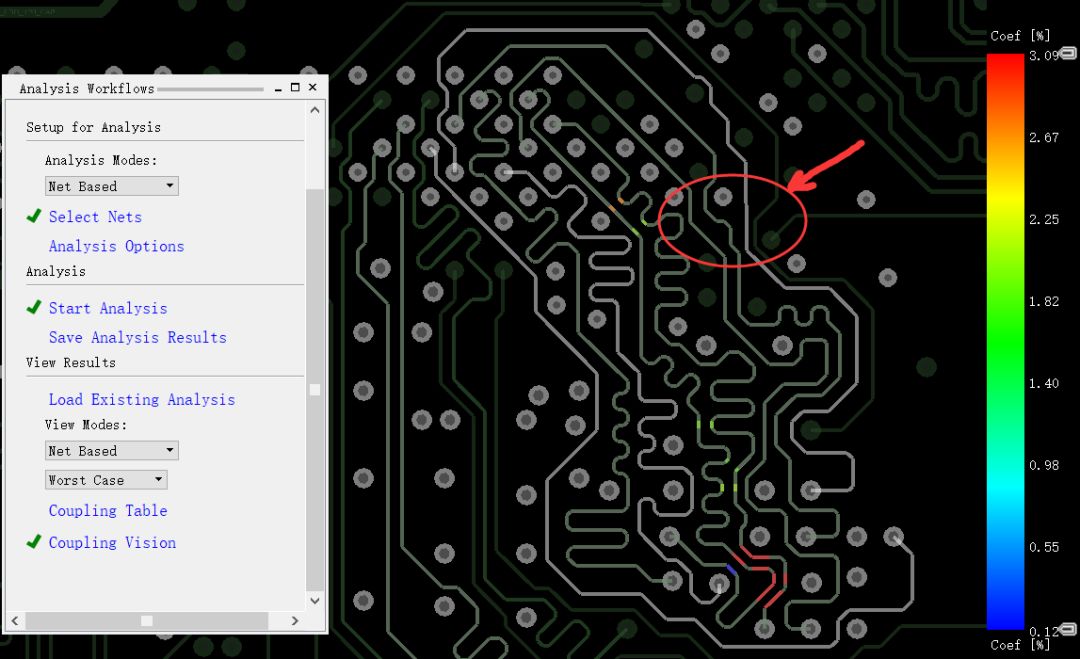

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

- 1

- 2

- 3

- 4

- 6

扫码关注

扫码关注

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第三部]](https://api.fanyedu.com/public/uploads/image/course/20200519/55b5b9f147397aa1097829400b322791.jpg)