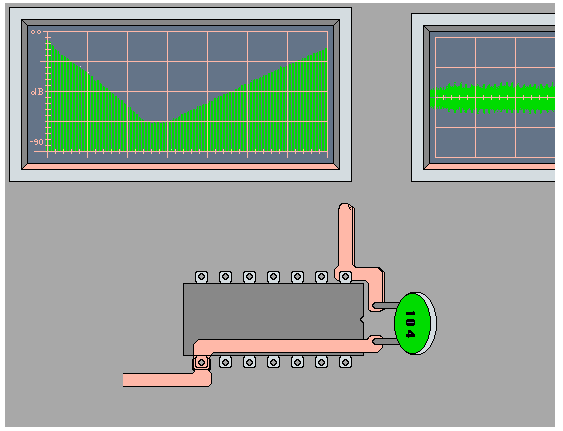

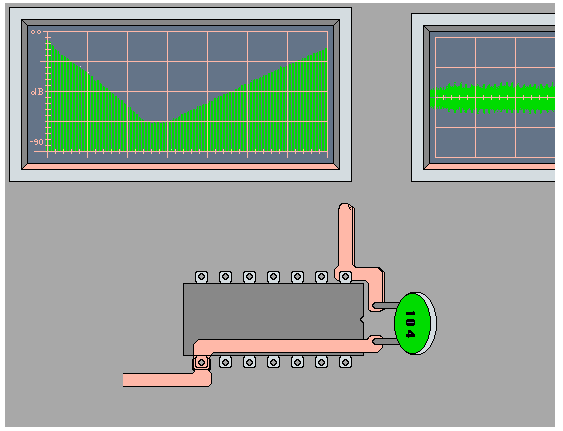

首先观察一个动图,了解去耦的概念以及一些注意事项,然后再对四个选项进行分析。

在电源引脚放置100nF的电容能够有效抑制电源上的噪声; “电源-去耦电容-地”三点一线的距离越近,则去耦的效果越好; 等容值SMD封装的电容比直插电容去耦效果好; 电源平面和地平面可以进一步降低电源噪声。

首先观察一个动图,了解去耦的概念以及一些注意事项,然后再对四个选项进行分析。

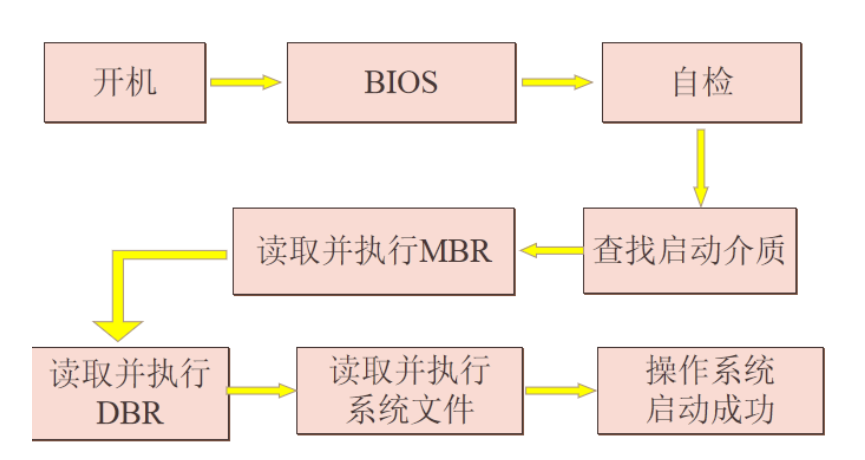

用户打开PC的电源,BIOS开机自检,按BIOS中设置的启动设备(通常是硬盘)启动,接着启动设备上安装的引导程序lilo或grub开始引导 Linux,... 详情>>

2024-03-27 11:32:57

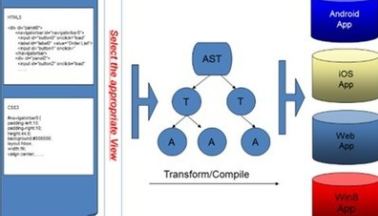

有时是因为⽬的平台上不允许或不能够安装我们所需要的编译器,⽽我们⼜需要这个编译器的某些特征;有时 是因为⽬的平台上的资源贫乏,⽆法运⾏我们所需要编译器;有时⼜是... 详情>>

2023-10-25 10:02:12

用户打开PC的电源,BIOS开机自检,按BIOS中设置的启动设备(通常是硬盘)启动,接着启动设备上安装的引导程序lilo或grub开始引导 Linux,Linu... 详情>>

2024-03-27 14:07:38

EMC设计工程师面试技巧EMC(Electromagnetic Compatibility)设计工程师的主要职责是确保电子设备在电磁环境中的正常运行,并且不会对... 详情>>

2023-11-27 11:44:26

HTTP协议永远都是客户端发起请求,服务器回送响应。1. GET 返回服务器针对特定资源所⽀持的HTTP请求⽅法。也可以利⽤向Web服务器发送'*'的请求来测试... 详情>>

2024-01-30 16:29:01