串扰对电子产品来说是非常麻烦的存在,它不仅影响产品性能,还会缩短电子产品的使用寿命,甚至可能引发事故造成经济生命损失,所以很多工程师都会在PCB电路设计中尽量采用缩小串扰危害性的设计技术,所以PCB电路设计中如何避免EMC串扰?

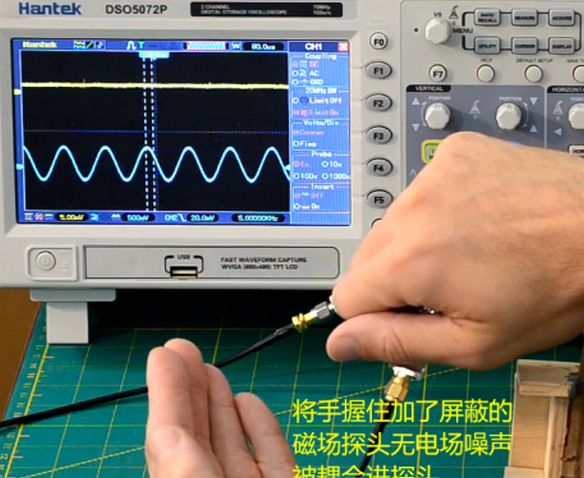

变化的信号(例如阶跃信号)沿传输线由A到B传播,传输线C-D上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且信号沿的变化(转换率)越快,产生的串扰也就越大。空间中耦合的电磁场可以提取为无数耦合电容和耦合电感的集合,其中由耦合电容产生的串扰信号在受害网络上可以分成前向串扰和反向串扰Sc,这个两个信号极性相同;由耦合电感产生的串扰信号也分成前向串扰和反向串扰SL,这两个信号极性相反。耦合电感电容产生的前向串扰和反向串扰同时存在,并且大小几乎相等,这样,在受害网络上的前向串扰。

信号由于极性相反,相互抵消,反向串扰极性相同,叠加增强。串扰分析的模式通常包括默认模式,三态模式和最坏情况模式分析。默认模式类似我们实际对串扰测试的方式,即侵害网络驱动器由翻转信号驱动,受害网络驱动器保持初始状态(高电平或低电平),然后计算串扰值。这种方式对于单向信号的串扰分析比较有效。三态模式是指侵害网络驱动器由翻转信号驱动,受害的网络的三态终端置为高阻状态﹐来检测串扰大小。这种方式对双向或复杂拓朴网络比较有效。最坏情况分析是指受害网络的驱动器保持初始状态,仿真器计算所有默认侵害网络对每一个受害网络的串扰的总和,这种方式一般只对个别关键网络进行分析,因为要计算的组合太多,仿真速度比较慢。

扫码关注

扫码关注